# unSP Programmer's Guide

V1.0 November 26, 2007

No.19, Industry E. Rd. IV, Hsinchu Science Park, Hsinchu City 30077, Taiwan, R.O.C. Tel: +886-3-666-2118 Fax: +886-3-666-2117 Web: www.generalplus.com

#### Important Notice

GENERALPLUS TECHNOLOGY INC. reserves the right to change this documentation without prior notice. Information provided by GENERALPLUS TECHNOLOGY INC. is believed to be accurate and reliable. However, GENERALPLUS TECHNOLOGY INC. makes no warranty for any errors which may appear in this document. Contact GENERALPLUS TECHNOLOGY INC. to obtain the latest version of device specifications before placing your order. No responsibility is assumed by GENERALPLUS TECHNOLOGY INC. for any infringement of patent or other rights of third parties which may result from its use. In addition, GENERALPLUS products are not authorized for use as critical components in life support devices/ systems or aviation devices/systems, where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user, without the express written approval of Generalplus.

# **Table of Content**

| 1 Introduction7                                                     |   |

|---------------------------------------------------------------------|---|

| 1.1 General Description7                                            |   |

| 1.2 Pin Diagram7                                                    |   |

| 1.2.1 Pin Diagram and Description of unSP-1.27                      |   |

| 1.2.2 Pin Diagram and Description of unSP-1.38                      | , |

| 1.2.3 Pin Diagram and Description of <i>unSP</i> -2.010             | 1 |

| 1.3 Features                                                        |   |

| 1.3.1 Features of unSP-1.0 and unSP-1.111                           |   |

| 1.3.2 Features of unSP-1.212                                        | , |

| 1.3.3 Features of unSP-1.313                                        |   |

| 1.3.4 Features of <i>unSP</i> -2.014                                | • |

| 1.4 Architecture16                                                  | ) |

| 1.4.1 Architecture of unSP-1.0 and unSP-1.1                         | ) |

| 1.4.2 Architecture of unSP-1.217                                    |   |

| 1.4.3 Peripheral Interface of unSP-1.218                            | , |

| 1.4.4 Architecture of unSP-1.320                                    | 1 |

| 1.4.5 Architecture of <i>unSP</i> -2.022                            | , |

| 1.4.6 Pipeline Feature of unSP-2.023                                |   |

| 1.5 Register24                                                      | • |

| 1.5.1 Register of unSP-1.0 and unSP-1.124                           |   |

| 1.5.2 Register of unSP-1.224                                        |   |

| 1.5.3 Register of <i>unSP</i> -1.3                                  | ) |

| 1.5.4 Registers of <i>unSP</i> - 2.0                                | , |

| 1.6 Memory                                                          |   |

| 1.6.1 Memory Map of unSP31                                          |   |

| 1.6.2 Memory Interface of unSP-1.231                                |   |

| 1.6.3 Memory Architecture of <i>unSP</i> -1.334                     |   |

| 1.6.4 Memory Architecture of unSP-2.0                               | ) |

| 1.6.5 Memory Interface of unSP-2.0                                  |   |

| 1.7 Addressing Modes43                                              | 1 |

| 1.7.1 6 addressing modes of <i>unSP</i> -1.0 and <i>unSP</i> -1.143 | 1 |

| 1.7.2 6 addressing modes of <i>unSP</i> -1.2 and <i>unSP</i> -2.0 | 44  |

|-------------------------------------------------------------------|-----|

| 1.7.3 9 addressing modes of <i>unSP</i> -1.3                      | 45  |

| 1.8 Interrupts                                                    | 46  |

| 1.8.1 Interrupts of <i>unSP</i> -1.0 and <i>unSP</i> -1.1         | 46  |

| 1.8.2 Interrupts of <i>unSP</i> -1.2                              | 47  |

| 1.8.3 Interrupts of <i>unSP</i> -1.3                              | 51  |

| 1.8.4 Interrupts of <i>unSP</i> -2.0                              | 54  |

| 1.9 Data Types                                                    | 60  |

| 1.10 ALU Operation Types                                          | 60  |

| 1.11 Conditional Branches                                         | 61  |

| 2 unSP- 1.1 Instruction Set                                       |     |

| 2.1 unSP Instructions Classification                              | 63  |

| 2.1.1 Notation                                                    | 63  |

| 2.1.2 Instruction Classification                                  | 64  |

| 2.2 <i>unSP</i> Instruction Format                                | 64  |

| 2.3 unSP-1.1 Instruction Set                                      | 66  |

| 2.3.1 Data-Transfer Instructions                                  | 66  |

| 2.3.2 Arithmetic/Logical-Operation Instructions                   | 70  |

| 2.3.3 Transfer-Control Instructions                               |     |

| 2.3.4 Miscellaneous Instructions                                  |     |

| 3 unSP -1.0 Instruction Set                                       |     |

| 3.1 General Description                                           |     |

| 3.2 <i>unSP</i> -1.0 Instruction Cycles                           |     |

| 4 unSP -1.2 Instruction Set                                       |     |

| 4.1 unSP-1.2 Instruction Set                                      |     |

| 4.1.1 Data-Transfer Instructions                                  |     |

| 4.1.2 Data Processing Instructions                                |     |

| 4.1.3 Data Segment Access Instruction                             |     |

| 4.1.4 Transfer-Control Instructions                               | 129 |

| 4.1.5 Miscellaneous Instructions                                  |     |

| 4.1.6 Instruction Set Summary                                     | 136 |

| 5 unSP-1.3 Instruction Set                                        | 138 |

| 5.1 unSP-1.3 Instruction Set                                      |     |

| 5.1.1 Byte Register Indirect                                      | 138 |

| 5.1.2 Byte Indexed Address                                  |

|-------------------------------------------------------------|

| 5.1.3 Byte Register Indexed Address139                      |

| 5.1.4 Special Register Access                               |

| 6 unSP-2.0 Instruction Set                                  |

| 6.1 unSP-2.0 Instruction Cycles143                          |

| 6.1.1 Data-Transfer Instructions143                         |

| 6.1.2 Data Processing Instructions144                       |

| 6.1.3 Data Segment Access Instruction153                    |

| 6.1.4 Transfer-Control Instructions154                      |

| 6.1.5 Miscellaneous Instructions156                         |

| 6.2 New Instructions of <i>unSP</i> -2.0 Instruction Set158 |

| 6.2.1 Data-Transfer Instructions158                         |

| 6.2.2 Data Processing Instructions161                       |

| 6.2.3 Instruction Set Summary170                            |

| 6.3 Stall Condition174                                      |

| 7 Appendix A Difference Between un SP - 1.2 & unSP- 1.3 179 |

| 8 Appendix B Difference Between un SP - 2.0 & unSP- 1.2     |

| 9 Appendix C Comparison Between unSP Versions               |

| 10 Appendix D CPU Cycle Formula and Examples                |

| c.1 unSP 1.2 Cycle Formula183                               |

| c.2 unSP 1.3 Cycle Formula                                  |

| c.2 unSP 2.0 Cycle Formula                                  |

# **Revision History**

| Revision | Date       | Revised By | Remark   |

|----------|------------|------------|----------|

| V1.0     | 2007/11/26 | Summer Yi  | Original |

# **1** Introduction

# **1.1 General Description**

The *unSP* pronounced as micro-n-S-P, is the first 16-bit microprocessor developed by Generalplus. Not only does the *unSP* perform general operations such as addition, subtraction and other logical operations, but it also supports multiplication and inner-product operations for digital signal processing. Now, the *unSP* has a series of version named *unSP* 1.0, *unSP* 1.1, *unSP* 1.2, *unSP* 1.3 and *unSP* 2.0.

# 1.2 Pin Diagram

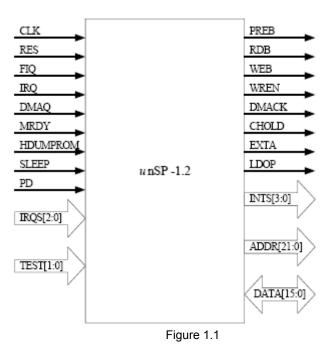

# 1.2.1 Pin Diagram and Description of unSP-1.2

#### Pin Diagram

#### Pin Description

| Name | I/O   | Description                     | Number |

|------|-------|---------------------------------|--------|

| CLK  | INPUT | External clock                  | 1      |

| RES  | INPUT | External reset                  | 1      |

| FIQ  | INPUT | Fast interrupt request          | 1      |

| IRQ  | INPUT | Normal interrupt request        | 1      |

| IRQS | INPUT | Normal interrupt request select | 3      |

| DMAQ | INPUT | DMA request                     | 1      |

| MRDY | INPUT | Memory data ready signal        | 1      |

| TEST | INPUT | Test mode select pins           | 2      |

| Name     | I/O    | Description                     | Number |

|----------|--------|---------------------------------|--------|

| HDUMPROM | INPUT  | Dump internal ROM to memory bus | 1      |

| SLEEP    | INPUT  | Sleep mode                      | 1      |

| PD       | INPUT  | Power down mode                 | 1      |

| ADDR     | OUTPUT | Address bus                     | 22     |

| PREB     | OUTPUT | Memory pre-charge signal        | 1      |

| RDB      | OUTPUT | Memory read enable signal       | 1      |

| WEB      | OUTPUT | Memory write enable signal      | 1      |

| WREN     | OUTPUT | Memory accessing mode           | 1      |

| DMACK    | OUTPUT | DMA acknowledge                 | 1      |

| CHOLD    | OUTPUT | CPU stall signal                | 1      |

| EXTA     | OUTPUT | Access data with DS             | 1      |

| LDOP     | OUTPUT | Fetch instruction into CPU      | 1      |

| INTS     | OUTPUT | CPU operation mode              | 4      |

| DATA     | INOUT  | Data bus                        | 16     |

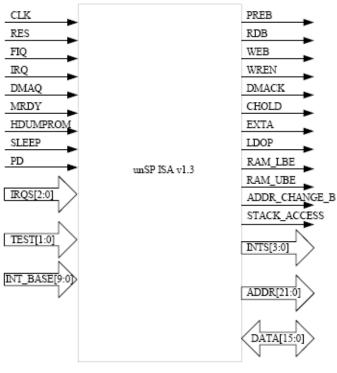

# 1.2.2 Pin Diagram and Description of unSP-1.3

#### Pin Diagram

Figure 1.2

#### Pin Description

Table 1.2

| Name          | I/O    | Description                          | Number |

|---------------|--------|--------------------------------------|--------|

| CLK           | INPUT  | External clock                       | 1      |

| RES           | INPUT  | External reset                       | 1      |

| FIQ           | INPUT  | Fast interrupt request               | 1      |

| IRQ           | INPUT  | Normal interrupt request             | 1      |

| IRQS          | INPUT  | Normal interrupt request select      | 3      |

| DMAQ          | INPUT  | DMA request                          | 1      |

| MRDY          | INPUT  | Memory data ready signal             | 1      |

| TEST          | INPUT  | Test mode select pins                | 2      |

| INT_BASE      | INPUT  | Interrupt vector base address        | 10     |

| HDUMPROM      | INPUT  | Dump internal ROM to memory bus      | 1      |

| SLEEP         | INPUT  | Sleep mode                           | 1      |

| PD            | INPUT  | Power down mode                      | 1      |

| ADDR          | OUTPUT | Address bus                          | 22     |

| RAM_LBE       | OUTPUT | Upper byte Enable                    | 1      |

| RAM_UBE       | OUTPUT | Lower byte Enable                    | 1      |

| ADDR_CHANGE_B | OUTPUT | Address change signal                | 1      |

| STACK_ACCESS  | OUTPUT | Indicate that CPU is accessing stack | 1      |

| PREB          | OUTPUT | Memory pre-charge signal             | 1      |

| RDB           | OUTPUT | Memory read enable signal            | 1      |

| WEB           | OUTPUT | Memory write enable signal           | 1      |

| WREN          | OUTPUT | Memory accessing mode                | 1      |

| DMACK         | OUTPUT | DMA acknowledge                      | 1      |

| CHOLD         | OUTPUT | CPU stall signal                     | 1      |

| EXTA          | OUTPUT | Access data with DS                  | 1      |

| LDOP          | OUTPUT | Fetch instruction into CPU           | 1      |

| INTS          | OUTPUT | CPU operation mode                   | 4      |

| DATA          | INOUT  | Data bus                             | 16     |

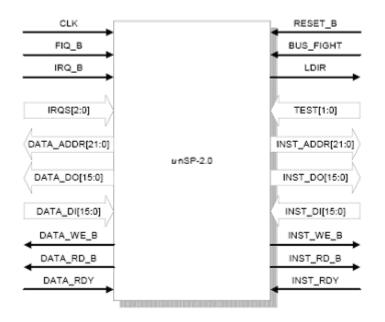

# 1.2.3 Pin Diagram and Description of unSP-2.0

#### Pin Diagram

Figure 1.3

# Pin Description

Table 1.3

| Name      | I/O    | Description                            | Number |

|-----------|--------|----------------------------------------|--------|

| CLK       | Input  | CPU clock                              | 1      |

| RESET_B   | Input  | CPU reset                              | 1      |

| FIQ_B     | Input  | Fast interrupt request (level trigger) | 1      |

| IRQ_B     | Input  | Interrupt request (level trigger)      | 1      |

| IRQS      | Input  | Interrupt request source               | 3      |

| TEST      | Input  | Test mode select                       | 2      |

| INST_ADDR | Output | Instruction Bus address                | 22     |

| INST_DI   | Input  | Instruction Bus data input             | 16     |

| INST_DO   | Output | Instruction Bus data output            | 16     |

| INST_RD_B | Output | Instruction Bus read enable signal     | 1      |

| INST_WE_B | Output | Instruction Bus write enable signal    | 1      |

| INST_RDY  | Input  | Instruction Bus ready signal           | 1      |

| DATA_ADDR | Output | Data Bus address                       | 22     |

| DATA_DI   | Input  | Data Bus data input                    | 16     |

| DATA_DO   | Output | Data Bus data output                   | 16     |

| DATA_RD_B | Output | Data Bus read enable signal            | 1      |

| DATA_WE_B | Output | Data Bus write enable signal           | 1 |

|-----------|--------|----------------------------------------|---|

| DATA_RDY  | Input  | Data Bus ready signal                  | 1 |

| BUS_FIGHT | Input  | Instruction Bus & Data Bus access same | 1 |

| LDIR      | Output | Load next instruction                  | 1 |

# 1.3 Features

# 1.3.1 Features of unSP-1.0 and unSP-1.1

- 16-bit micro controller with DSP function

- Memory bus interface

- Address width: 22-bit

- Data width: 16-bit

- 4M words (8M bytes) memory space

- 64 banks/ 64k words per bank

- 8\*16-bit registers

- 4 general registers (R1~R4)

- 4 system registers (SP, BP, SR, PC)

- 10 interrupts

- 1 fast interrupt (FIQ)

- 8 normal interrupt (IRQ0-IRQ7)

Software interrupt (BRK)

- 6 addressing modes

- Register Direct(R)

- Register Indirect ([R])

- Immediate (IM6/IM16)

- Memory Absolute Address ([A6]/ [A16]/ [A22]) Indexed Address ([BP+IM6])

- PC Relatively (PC+IM6)

- 16-bit multiplication

- 2 operation modes: signed\*signed, unsigned\*signed

- 16-levels inner product operation

- 2 operation modes: signed\*signed, unsigned\*signed

- 4 guard bits to avoid overflow

Difference between unSP -1.0 and unSP- 1.1

*UnSP* - 1.1 is an enhanced version of *unSP* -1.0. The behaviors of CS and DS registers are changed to facilitate large program execution and large data access.

Table 1.4

|                                         | UnSP <b>1.0</b> | unSP <b>1.1</b>                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GOTO instruction                        |                 | The target address can be any address in the 4M words memory (22-bit).                                                                                                                                                                                                                                                 |

| CS register<br>auto-increment/decrement | N/A             | <ol> <li>New feature</li> <li>During program execution, PC will be<br/>incremented by one continuously. If a carry<br/>takes place, CS will be incremented by one.</li> <li>Branch instruction versus PC is based on<br/>the combination of CS and PC. The result<br/>will be stored back to the CS and PC.</li> </ol> |

| DS register<br>auto-increment/decrement | N/A             | <ol> <li>New feature.</li> <li>In indirect addressing mode, if the D:[++Rs] /<br/>D:[Rs++] / D:[Rs] are used, these<br/>operations are executed based on the 22-bit<br/>register arithmetic and the final result is<br/>stored back to DS and RS.</li> </ol>                                                           |

| Instruction cycles                      |                 | Generally speaking, most instruction cycles are faster than <i>unSP</i> 1.0.                                                                                                                                                                                                                                           |

# 1.3.2 Features of unSP-1.2

- 16-bit micro controller with DSP function

- Memory bus interface

- Address width: 22-bit

- Data width: 16-bit

- 4M words (8M bytes) memory space

- 64 banks/ 64k words per bank

- 13\*16-bit registers

- 4 general registers (R1~R4)

- 4 secondary registers (SR1~SR4)

- 4 system registers (SP, BP, SR, PC)

- 1 flag register (FR)

- 10 interrupts

- 1 fast interrupt (FIQ)

- 8 normal interrupt (IRQ0-IRQ7)

- Support IRQ nested mode with user customized priority

- Software interrupt (BRK)

- 6 addressing modes

- Register

- Immediate

- Direct

- Indirect

- Multi-indirect

- Displacement

- 16-bit multiplication

- 3 operation modes: signed\*signed, unsigned\*signed, unsigned\*unsigned

- Integer/Fraction mode

- 16-levels inner product operation

- 3 operation modes: signed\*signed, unsigned\*signed, unsigned\*unsigned

- Integer/Fraction mode

- 4 guard bits to avoid overflow

- Non-restoring Division

- 32-bit dividend and 16-bit divisor

- Need 16 continuous operations (DIVS, DIVQ) to generate correct quotient

- Bit-operation

- Bit test/ set/ clear/ inverse operation

- Destination can be register or memory

- Effective-exponent detect operation

- 16-bit shift operation

Support 32-bit shift operation by combining 2 shift instructions

- Support DMA function

- Support power down/sleep mode

# 1.3.3 Features of unSP-1.3

The most significant difference between *unSP* 1.2 and *unSP* 1.3 is the byte addressing modes in *unSP*1.3.

- 16-bit micro controller with DSP function

- Memory bus interface

- Address width: 22-bit

- Data width: 16-bit

- 4M words (8M bytes) memory space

- 64 banks/ 64k words per bank

- Byte accessing-mechanism with new addressing mode

- 14\*16-bit and 1\*6-bit registers

- 4 general registers (R1~R4)

- 4 secondary registers (SR1~SR4)

- 6 system registers (SS, MDS, SP, BP, SR, PC)

- 1 flag register (FR)

- 10 interrupts

- 1 fast interrupt(FIQ)

- 8 normal interrupt(IRQ0-IRQ7)

- Support IRQ nested mode with user customized priority

- Software interrupt (BRK)

- 9 addressing modes

- Register

- Immediate

- Direct

- Indirect

- Multi-indirect

- Displacement

- Byte register indirect

- Byte indexed address

- Byte register indexed address

- 16-bit multiplication

- 3 operation modes: signed\*signed, unsigned\*signed, unsigned\*unsigned

- Integer/Fraction mode

- 16-levels inner product operation

- 3 operation modes: signed\*signed, unsigned\*signed, unsigned\*unsigned

- Integer/Fraction mode

- 4 guard bits to avoid overflow

- Non-restoring Division

- 32-bit dividend and 16-bit divisor

- 16 continuous operations (DIVS, DIVQ) or only one operation (DIVSS, DIVUU) to generate correct quotient.

- Bit-operation

- Bit test/ set/ clear/ inverse operation

- Destination can be register or memory

- 2 address mode (direct, indirect) for memory access.

- Effective-exponent detect operation

- 16-bit shift operation

- Support 32-bit shift operation by combining 2 shift instructions

- Support DMA function

- Support power down/sleep mode

# 1.3.4 Features of *unSP*-2.0

16-bit micro controller with DSP function

- *unSP 1.2* binary compatible

- Modified Harvard architecture

- Instruction memory bus (IM): addr: 22-bit / data: 16-bit

- 64 banks / 64k words per bank

- Data memory bus (DM): addr: 22 bits / data: 16-bit

64 banks / 64k words per bank

- 2 configurations

- IM/DM share 4M words memory space (default)

- IM/DM own separate 4M words memory space (Not recommended. Assembler and linker do not support overlapped address of IM and DM.)

- 4-stage pipelined architecture

- IF (Instruction Fetch)

- DE (Decode)

- MR (Memory Read Access)

- EX/MW (Execution/Memory Write)

- 21\*16-bit registers

- 4 general registers (R1-R4)

- 4 secondary-bank registers for interrupt (SR1-SR4)

- 1 base address register (BP)

- 3 system registers (SP, SR, PC)

- 1 inner flag register (FR)

- 8 extended registers (R8-R15)

- 10 interrupt sources

- 1 fast interrupt (FIQ)

- 8 normal interrupts (IRQ)

- 1 software interrupt (BRK)

- Support IRQ nested mode with priority

- 6 addressing modes

- Register

- Immediate (I6/I16)

- Direct (A6/A16)

- Indirect + auto indexing address (DS indirect)

- Displacement (BP+IM6)

- Multiple indirect (PUSH/POP)

- 16-bit multiplication

- 3 operation modes: signed\*signed, unsigned\*signed, unsigned\*unsigned

- Integer / Fraction modes

- 16-levels inner product operation

- 1 cycle MAC (multiplier/accumulator) unit

- 3 operation modes: signed\*signed, unsigned\*signed, unsigned\*unsigned

- 4 guard bits to avoid overflow

- Integer / Fraction modes

- Non-restoring division

- 32-bit dividend and 16-bit divisor

- Need 16 continuous operations (DIVS, DIVQ) to generate correct quotient

- Effective-exponent detect operation

- Bit operations

- Support 4 operations: test, set, clear, inverse.

- Destination can be register or memory.

- 2 address mode (direct, indirect) for memory access.

- 16-bit shift operation

- 1 cycle log-shifter

- Support 32-bit shift operation by combining 2 shift instructions.

# **1.4 Architecture**

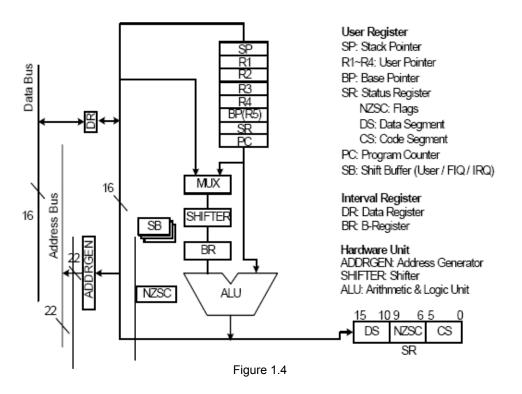

# 1.4.1 Architecture of unSP-1.0 and unSP-1.1

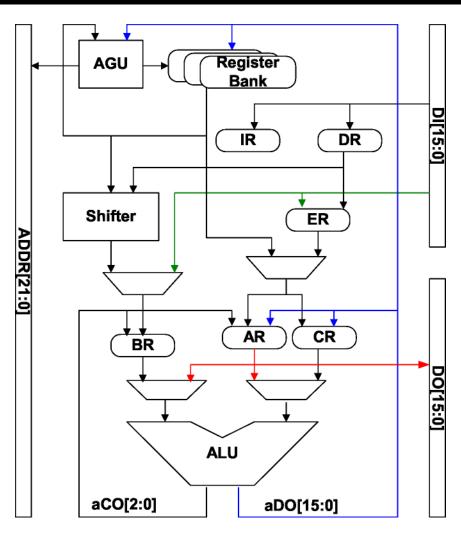

The design goal of unSP 1.0 and unSP 1.1 is to achieve high performance with low cost. It uses the traditional multi-cycle architecture. The organization of unSP 1.0 and unSP 1.1 is illustrated as below. The principal components are:

- The general registers (R1-R4) and the system registers (SP, BP, SR, PC) in the register bank.

- The data register (DR), which store the data.

- The address generator unit (AGU), which selects and holds all memory address and generate sequential address when required.

- The shifter, which can shift or rotate one operand by any number of 4-bit.

- The ALU, which performs the arithmetic and logic functions required by current instruction.

# 1.4.2 Architecture of unSP-1.2

The design goal of *unSP* 1.2 is to achieve high performance with low cost. It uses the traditional multi-cycle architecture. The organization of *unSP* 1.2 is illustrated as below. The principal components are:

- The register bank, which stores the processor state. There are 4 general registers (R1-R4), 4 secondary bank registers (SR1-SR4), 4 system registers (SP, BP, SR, PC) and 1 flag register (FR) in the register bank.

- The instruction register (IR), which store the current instruction fetched from data bus. The decoder will generate all control signals for data path according to the instruction register.

- The data register (DR), which store the second word of current instruction if instruction length is 2 words.

- The address generator unit (AGU), which selects and holds all memory address and generate sequential address when required.

- The shifter, which can shift or rotate one operand by any number of 4-bit.

- The ALU, which performs the arithmetic and logic functions required by current instruction.

Figure 1.5

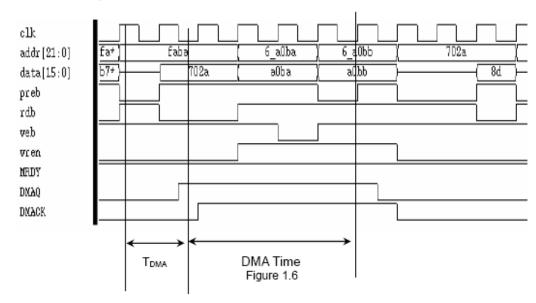

# 1.4.3 Peripheral Interface of unSP-1.2

# DMA Timing

- DMAQ: DMA request, active high.

- DMACK: when CPU accept DMA request from DMAQ, it will reply DMACK signal and release address, data bus, preb, web, rdb, wren signals after last memory access.

The longest delay without memory waiting cycle from DMAQ request to DMACK reply  $T_{DMA} \le 3$  clock cycles (max cycles for instruction to access memory)

- CK: CPU internal clock.

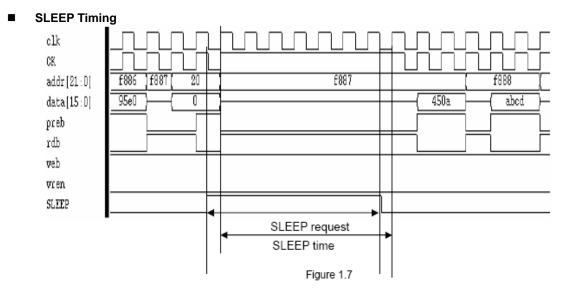

- SLEEP will stall the CPU clock at high and keep address, data, preb, rdb, web, wren at origin value.

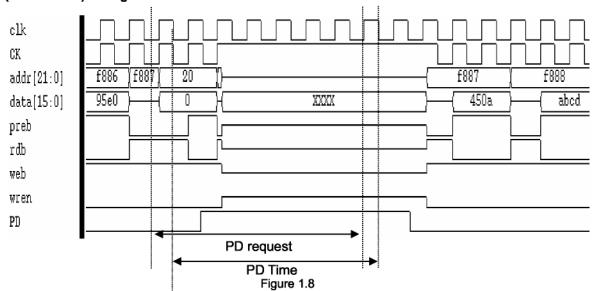

PD (Power Down) Timing

PD will stall the CPU clock at high and release the address, data bus, preb, rdb, web, wren signals.

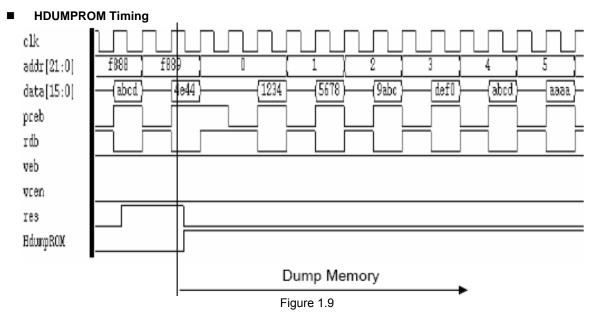

HdumpROM is used to dump memory content from current address. If you want to dump all memory content to data bus, you can use RESET and HdumpROM signal. After reset and keep HdumpROM at high, the memory content from 0x000000 ~ 0x3FFFFF will be dumped to memory bus contiguously every 2 cycles.

# 1.4.4 Architecture of unSP-1.3

The design goal of *unSP* 1.3 is to achieve high performance with low cost. It uses the traditional multi-cycle architecture. The organization of *unSP* 1.3 is illustrated as below. The principal components are:

- The register bank, which stores the processor state. There are 4 general registers (R1-R4), 4 secondary bank registers (SR1-SR4), 6 system registers (SS, SP, MDS, BP, SR, PC) and 1 flag register (FR) in the register bank.

- The instruction register (IR), which store the current instruction fetched from data bus. The decoder will generate all control signals for data path according to the instruction register.

- The data register (DR), which store the second word of current instruction if instruction length is 2 words.

- The address generator unit (AGU), which selects and holds all memory address and generate sequential address when required.

- The shifter, which can shift or rotate one operand by any number of 4-bits.

- The ALU, which performs the arithmetic and logic functions required by current instruction.

Figure 1.10

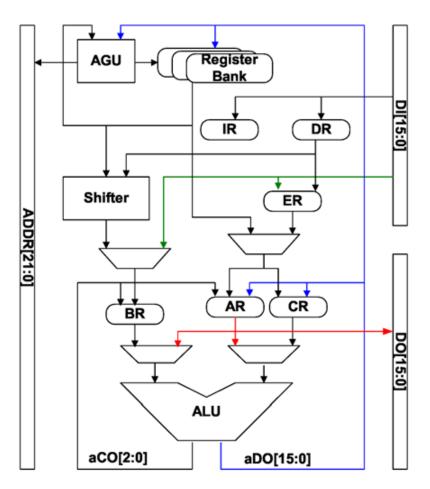

# 1.4.5 Architecture of *unSP*-2.0

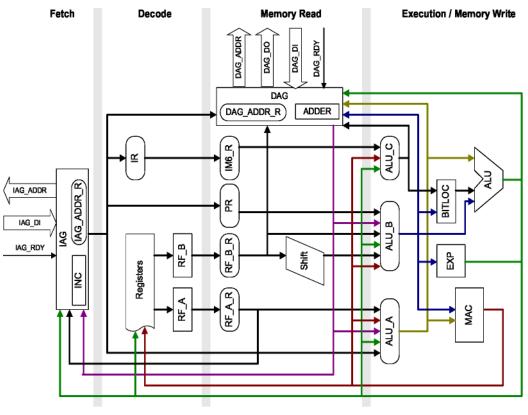

*unSP*–2.0 is a 4-stage pipeline architecture. Its organization is illustrated as below. The principal components are:

- The register bank, which stores the processor state. There are 4 general registers (R1-R4), 4 secondary bank registers (SR1-SR4), 4 system registers (SP, BP, SR, PC), 8 extend registers (R8~R15) and 1 flag register (FR) in the register bank.

- The instruction register (IR), which stores the current instruction fetched from instruction bus. The decoder will generate all control signals for data path according to the instruction register.

- The parameter register (PR), which stores the second word of current instruction if instruction length is 2 words.

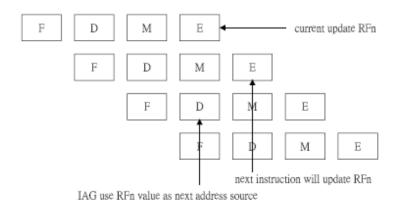

- The instruction address generator unit (IAG), which selects and holds all instruction address and generate sequential address when required.

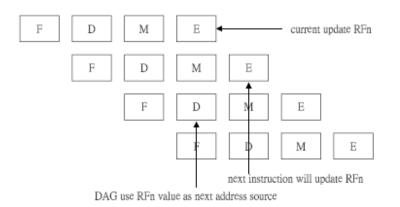

- The data address generator unit (DAG), which generate and hold all data address.

- The Shifter, which can shift or rotate one operand by any number of 4-bit.

- The ALU, which performs the arithmetic and logic functions required by current instruction.

- The MAC, which performs the multiplication and accumulate functions required by current instruction.

Figure 1.11

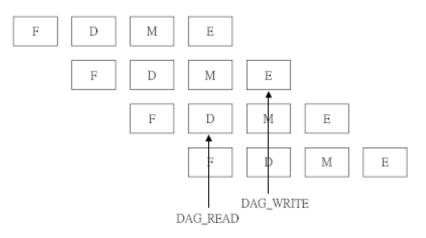

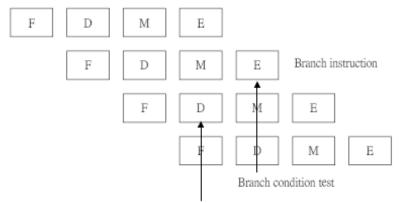

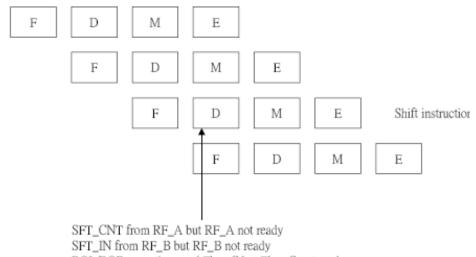

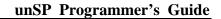

# 1.4.6 Pipeline Feature of unSP-2.0

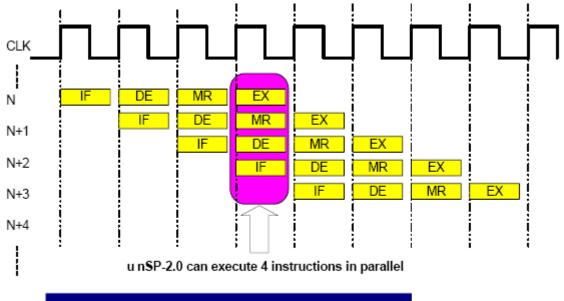

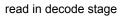

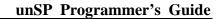

*unSP* 2.0 employs a simple 4-stage pipeline with the following pipeline stages:

Fetch:

The instruction is fetched from memory and placed in the instruction registers.

Decode:

The instruction is decoded and the data-path control signals prepared for the next cycle. If current instruction needs to read data from memory, the access address will be generated and issued in this stage.

Memory Read:

Waiting state for memory read access. If current instruction needs performing shift operation, it will be done in this stage.

Execution / Memory Write:

All ALU operations, multiplication are executing in this stage and the result will be write back to register or memory at the next cycle, if current instruction need to write data to memory, the access address will be generated and issued in this stage.

At any one time, four different instructions may occupy each of these stages

Figure 1.12

# 1.5 Register

# 1.5.1 Register of unSP-1.0 and unSP-1.1

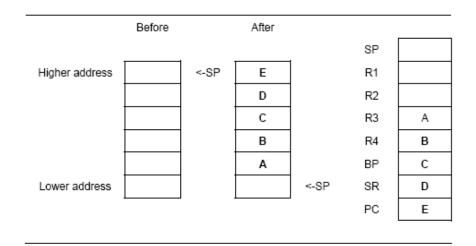

*unSP* 1.0 and *unSP* 1.1 have eight 16-bit registers: Stack Pointer (SP), User Registers (R1, R2, R3, R4), Based Pointer (BP), Status Register (SR) and Program Counter (PC). Please see Table 1.5 for details. The concatenation of R3 and R4 forms a 32-bit register, MR, which is used as the destination register for multiplication and inner-production. The Stack Pointer (SP) automatically increases (POP) or decreases (PUSH) as the *unSP* performing push/pop, subroutine call or interrupt operations. The stack size is limited to 64K, i.e., 0x000000 ~ 0x00FFFF. Since *unSP* 1.0 and *unSP* 1.1 are able to address 4M-word locations, additional 6 bits are needed to construct a 22-bit address from a 16-bit register for fetching instructions (OP codes) and data accessing purposes. These 6 bits reside in the SR register, which contains the Code Segment (CS) and the Data Segment (DS) fields. Therefore, both code addresses and data addresses can be represented in 22 bits.

In *unSP* 1.0, the value in CS will not be changed by sequential execution and conditional branch when crossing page boundaries. This behavior limits each code section cannot be larger than 64K words. Only call instruction and interrupts can change CS. The DS will not be changed by pre-increment addressing, post-increment addressing and post-decrement addressing modes. This behavior limits each data section cannot be larger than 64K words. For example, suppose CS is 0x03 and PC is 0xFFFF, the next instruction fetched by the *unSP* is located at CS:PC = 0x030000, not 0x040000.

In *unSP* 1.1, the content of total 22 bits formed by CS or DS and a register will be changed accordingly when crossing page boundaries. Thus the 64K limitation is removed.

| Register ID | Name    |

|-------------|---------|

| 0 (000)     | SP      |

| 1 (001)     | R1      |

| 2 (010)     | R2      |

| 3 (011)     | R3      |

| 4 (100)     | R4      |

| 5 (101)     | BP (R5) |

| 6 (110)     | SR      |

| 7 (111)     | PC      |

| Table 1.5 unSP 1.0 and | d unSP 1.1 Registers |

|------------------------|----------------------|

|------------------------|----------------------|

# 1.5.2 Register of unSP-1.2

#### Registers Bank

*unSP* 1.2 adds 4 registers (SR1~SR4) for interrupt service routines to reduce the push/pop effort. User can use SECBANK On/Off instruction to switch register bank. If SECBANK mode is on, all

| <u>PRIBANK</u>                            | <u>SECBANK</u> ≁         |

|-------------------------------------------|--------------------------|

| 000. SP↩<br>Bla                           | <sup>000</sup> SP₽       |

| 001 <u>, R1</u> ↔<br>010, R2↔             | 001. SR1↔<br>010. SR2↔   |

| 011 <u>, R3</u> ₽<br>R4₽                  | ont SR3↔<br>SR3↔<br>SR4↔ |

|                                           | ., <b>BP</b> ₄⊃          |

| $\frac{\mathbf{SR}^{2}}{\mathbf{PC}^{2}}$ | in SR@                   |

| FR                                        | FR↔                      |

are not affected by the SECBANK On/Off instruction.

access to R1~R4 will be redirected to SR1~SR4. The other registers, SP, BP, SR, PC and FR,

- Primary Bank

- Stack Pointer (SP)

- General Register (R1~R4)

- Base Pointer (BP)

- Status Register (SR)

- Program Counter (PC)

- Flag Register (FR)

- Secondary Bank

- Secondary Register (SR1~SR4)

#### Status Register (SR)

| F | Е | D | С | В | А | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|   |   | D | S |   |   | Ν | Z | S | С |   |   | С | S |   |   |

- Conditional Flag

- N: Negative flag, denotes the 16th bit of ALU result.

- Z: Zero flag, denotes whether the ALU result is zero.

- S: Sign flag, denotes the MSB(18th) bit of ALU result.

- C: Carry flag, denotes the 17th bit of ALU result

- Data Segment (DS)

- Data segment can be used to access memory large than 64K words memory space

- Code Segment (CS)

- Code segment can be used to fetch instruction location large than 64K words memory space

- Code segment and Data segment will be updated automatically when the target address

#### crossing segment boundary.

#### Flag Register (FR)

| - | -  | • • |     |     |   |   |   |   |     |     |     |   |   |    |   |

|---|----|-----|-----|-----|---|---|---|---|-----|-----|-----|---|---|----|---|

| F | Е  | D   | С   | В   | А | 9 | 8 | 7 | 6   | 5   | 4   | 3 | 2 | 1  | 0 |

| - | AQ | BNK | FRA | FIR |   | S | В |   | FIQ | IRQ | INE |   | Р | RI |   |

- AQ: DIVS/DIVQ AQ flag, default is 0.

- BNK: Register bank, default is 0 (PRIBANK).

- FRA: Fraction mode, default is 0 (OFF).

- FIR: FIR move mode, default is 0 (FIR\_MOVE ON).

- SB: Shift buffer/guard bits, default is 4'b0000.

- FIQ: FIQ Enable, default is 0 (Disable)

- IRQ: IRQ Enable, default is 0 (Disable)

- INE: IRQ nest mode, default is 0 (OFF)

- PRI: IRQ priority register, default is 4'b1000 after reset. If IRQ nest mode is On and any IRQ occurred, PRI register will be set as the IRQ priority before CPU executing IRQ service routine. Only the IRQ with higher priority can interrupt it. User can customize the IRQ nest behavior by setting the priority register.

- Priority: IRQ0 > IRQ1 > IRQ2 > IRQ3 > IRQ4 > IRQ5 > IRQ6 > IRQ7

Note: FIQ still has highest priority than any IRQ if FIQ is enabled.

For example:

- If PRI is 4'b1000, IRQ0-7 are enabled

- If PRI is 4'b0000, IRQ0-7 are disabled

- If IRQ3 occurred, PRI will be set to 0011. Only IRQ0-2 are enabled.

#### 1.5.3 Register of unSP-1.3

#### Registers Bank

As *unSP* 1.2, *unSP* 1.3 contains 4 registers (SR1~SR4) for interrupt service routine to reduce the push/pop effort. User can use SECBANK On/Off instruction to switch register bank. If SECBANK mode is on, all access to R1~R4 will be redirected to SR1~SR4. The other registers, SP, BP, SR, PC, FR, SS and MDS, are not affected by the SECBANK On/Off instruction.

| 2   | PRIBANK | 5   | SECBANK |

|-----|---------|-----|---------|

| 000 | SP      | 000 | SP      |

| 001 | Rl      | 001 | SR1     |

| 010 | R2      | 010 | SR2     |

| 011 | R3      | 011 | SR3     |

| 100 | R4      | 100 | SR4     |

|     | BP      | 100 | BP      |

| 101 | SR      |     | SR      |

| 110 | PC      | 110 | PC      |

| 111 |         | 111 |         |

| [   | FR      |     | FR      |

| [   | SS      |     | SS      |

| [   | MDS     |     | MDS     |

- Primary Bank

- Stack Pointer (SP)

- General Register (R1~R4)

- Base Pointer (BP)

- Status Register (SR)

- Program Counter (PC)

- Flag Register (FR)

- Stack Segment Register (SS)

- Inner Product Operation Data Segment (MDS)

- Secondary Bank

- Secondary Register (SR1~SR4)

#### Status Register (SR)

| F | Е | D | С | В | А | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|   |   | D | S |   |   | Ν | Z | S | С |   |   | С | S |   |   |

• Conditional Flag

- N: Negative flag, denotes the 16th bit of ALU result.

- Z: Zero flag, denotes whether the ALU result is zero.

- S: Sign flag, denotes the MSB(18th) bit of ALU result.

- C: Carry flag, denotes the 17th bit of ALU result

- Data Segment (DS)

- Data segment can be used to access memory large than 64K words memory space

- Code Segment (CS)

- Code segment can be used to fetch instruction location large than 64K words memory

space

• Code segment and Data segment will be updated automatically when the target address crossing segment boundary.

#### Flag Register (FR)

| F   | Е  | D   | С   | В   | А | 9 | 8 | 7 | 6   | 5   | 4   | 3 | 2 | 1  | 0 |

|-----|----|-----|-----|-----|---|---|---|---|-----|-----|-----|---|---|----|---|

| AdE | AQ | BNK | FRA | FIR |   | S | В |   | FIQ | IRQ | INE |   | Р | RI |   |

- Ade: Byte-mode instruction address alignment error.

- AQ: DIVS/DIVQ AQ flag, default is 0.

- BNK: Register bank, default is 0 (PRIBANK).

- FRA: Fraction mode, default is 0 (OFF).

- FIR: FIR MOVE mode, default is 0 (FIR Move On).

- SB: Shift buffer/guard bits, default is 4'b0000.

- FIQ: FIQ Enable, default is 0 (Disable)

- IRQ: IRQ Enable, default is 0 (Disable)

- INE: IRQ nest mode, default is 0 (OFF)

- PRI: IRQ priority register, default is 4'b1000 after reset. If IRQ nest mode is On and any IRQ occurred, PRI register will be set as the IRQ priority before CPU executing IRQ service routine. Only the IRQ with higher priority can interrupt it. User can customize the IRQ nest behavior by setting the priority register.

- Priority: IRQ0 > IRQ1 > IRQ2 > IRQ3 > IRQ4 > IRQ5 > IRQ6 > IRQ7

Note: FIQ still has highest priority than any IRQ if FIQ is enabled.

- For example:

- If PRI is 4'b1000, IRQ0-7 are enabled

- If PRI is 4'b0000, IRQ0-7 are disabled

- If IRQ3 occurred, PRI will be set to 0011. Only IRQ0-2 are enabled.

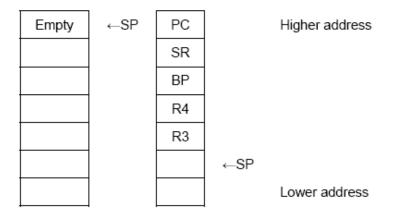

#### Stack Segment Register

The stack segment register (SS) is added to expand the size of stack. The size of SS is 6 bits. After reset, all bits of SS are cleared to be zero. The behavior of following stack related operations are changed.

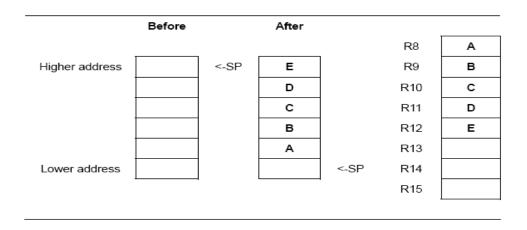

● PUSH R<sub>H</sub>, R<sub>L</sub> to [Rs]

The destination where  $R_{H} \sim R_{L}$  are pushed in a 22-bit address: {SS:Rs}<sub>21~0</sub>. That is, higher 6 bits in SS and lower 16 bits in Rs. After the push operation, {SS:Rs}<sub>21~0</sub> is decremented by the number of registers pushed.

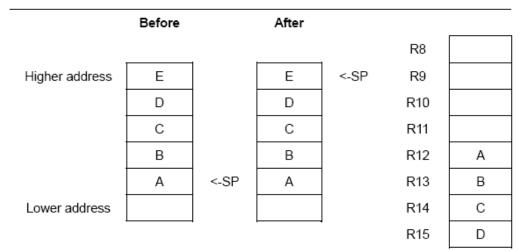

- POP RL, RH from [Rs] Increment {SS:Rs}<sub>21~0</sub> by 1. Move the content at {SS:Rs}<sub>21~0</sub> to Rx. Increment {SS:Rs}<sub>21~0</sub> by 1.Move the content at {SS:Rs}<sub>21~0</sub> to RL +1. Repeat these operations (RH – RL + 1) times.

- The effective address of [BP+n] addressing mode

The effective address is  $\{SS:Rs\}_{21\sim0}$  +n. Move the content at  $\{SS:Rs\}_{21\sim0}$  to Rx. Increment  $\{SS:Rs\}_{21\sim0}$  by 1.Move the content at  $\{SS:Rs\}_{21\sim0}$  to  $R_{L}$  +1. Repeat these operations ( $R_{H} - R_{L} + 1$ ) ti mes.

If SS is zero, the behaviors of these operations are the same as before.

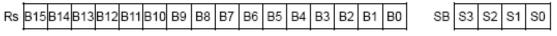

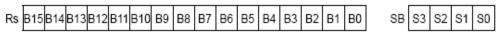

Inner Product Operation Data Segment Register (MDS)

| F | Е | D | С         | В | А | 9 | 8 | 7 | 6 | 5 | 4 | 3   | 2     | 1 | 0 |

|---|---|---|-----------|---|---|---|---|---|---|---|---|-----|-------|---|---|

| 0 | 0 |   | SEG of Rd |   |   |   |   |   |   |   |   | SEG | of Rs |   |   |

- Inner product operation data segment (MDS) are added to specify the page numbers of the two sources, Rd and Rs.

- The data of the two sources can cross the page boundary. When doing the MULS operation, the Rd and Rs will be added one by one. The carry signal will propagate to these MDS. This causes that the MDS are added by one when the value of Rd and Rs change from 0xFFFF to 0x0000.

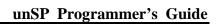

# 1.5.4 Registers of unSP-2.0

Normal mode

There are 3 system registers (SP, SR, PC), 4 general registers (R1~R4) and 1 flag registers (FR) can be used in normal mode for user program operation.

#### Registers Bank

4 secondary bank registers (SR1~SR4) are added for interrupt service routines to reduce the push/pop effort. User can use SECBANK On/Off instruction to switch register bank. If SECBANK mode is on, all access to R1~R4 will be redirected to SR1~SR4.

#### Extend Registers

*unSP* 2.0 add 8 extend registers (R8~R15) to reduce register swapping effort while executing complicity operations to improve performance, 8 extend instruction types are also added to do ALU operation between extend registers and memory or original registers sets (R0~PC).

- Primary Bank

- Stack Pointer (SP)

- General Register (R1~R4)

- Base Pointer (BP)

- Status Register (SR)

- Program Counter (PC)

- Flag Register (FR)

- Extend Register (R8~R15)

- Secondary Bank

- Secondary Register (SR1~SR4)

| PRIBANK | <u>SECBANK</u> |

|---------|----------------|

| SP      | SP             |

| Rl      | SR1            |

| R2      | SR2            |

| R3      | SR3            |

| R4      | SR4            |

| BP      | BP             |

| SR      | SR             |

| PC      | PC             |

| R8      | R8             |

| R9      | R9             |

| R10     | R10            |

| R11     | R11            |

| R12     | R12            |

| R13     | R13            |

| R14     | R14            |

| R15     | R15            |

| FR      | FR             |

Figure 1.15

# Status Register (SR)

| F | Е | D | С | В | А | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|   |   | D | S |   |   | Ν | Z | S | С |   |   | С | S |   |   |

- Conditional Flag

- N: Negative flag, denotes the 16th bit of ALU result.

- Z: Zero flag, denotes whether the ALU result is zero.

- S: Sign flag, denotes the MSB(18th) bit of ALU result.

- C: Carry flag, denotes the 17th bit of ALU result

- Data Segment (DS)

- Data segment can be used to access memory large than 64K words memory space

- Code Segment (CS)

- Code segment can be used to fetch instruction location large than 64K words memory space

- Code segment and Data segment will be updated automatically when the target address crossing segment boundary.

#### Flag Register (FR)

| F | Е  | D   | С   | В   | А | 9 | 8 | 7 | 6   | 5   | 4   | 3 | 2  | 1  | 0 |

|---|----|-----|-----|-----|---|---|---|---|-----|-----|-----|---|----|----|---|

| - | AQ | BNK | FRA | FIR |   | S | В |   | FIQ | IRQ | INE |   | PI | RI |   |

- AQ: DIVS/DIVQ AQ flag, default is 0.

- BNK: Register bank, default is 0 (PRIBANK).

- FRA: Fraction mode, default is 0 (OFF).

- FIR: FIR MOVE mode, default is 0 (FIR Move On).

- SB: Shift buffer/Guard bits, default is 4'b0000.

- FIQ: FIQ Enable, default is 0 (Disable)

- IRQ: IRQ Enable, default is 0 (Disable)

- INE: IRQ nest mode, default is 0 (OFF)

- PRI: IRQ priority register, default is 4'b1000 after reset. If IRQ nest mode is On and any IRQ occurred, PRI register will be set as the IRQ priority before CPU executing IRQ service routine. Only the IRQ with higher priority can interrupt it. User can customize the IRQ nest behavior by setting the priority register.

Priority: IRQ0 > IRQ1 > IRQ2 > IRQ3 > IRQ4 > IRQ5 > IRQ6 > IRQ7

Note: FIQ still has highest priority than any IRQ if FIQ is enabled.

For example:

- If PRI is 4'b1000, IRQ0-7 are enable

- If PRI is 4'b0000, IRQ0-7 are disable

- If IRQ3 occurred, PRI will be set to 0011. Only IRQ0-2 are enable.

# 1.6 Memory

# 1.6.1 Memory Map of unSP

The address map of *unSP* is divided by every 64K words (64K x 16 bits), called a page. The first page, PAGE0, corresponds to A[21:16]=0. The 4M-word (4096K) memory can be divided into total of 64 pages by A [21:16]=0x00 ~ 0x3F. The selection of page is defined by either a 6-bit Code Segment (CS) or 6-bit Data Segment (DS) in Status Register (SR), depends on execution opcode fetching or data accessing respectively. In memory mapping, PAGE0 is designed for storing data that is frequently accessed, e.g. working memory or peripherals. The other pages (non-zero pages) are designed for storing program codes or large chunk of data.

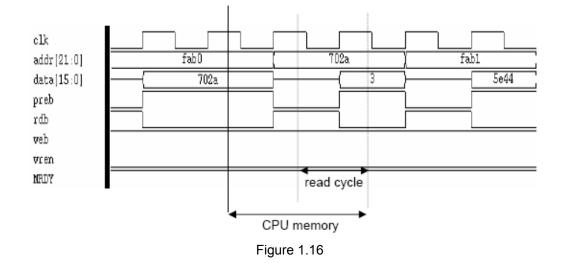

# 1.6.2 Memory Interface of unSP-1.2

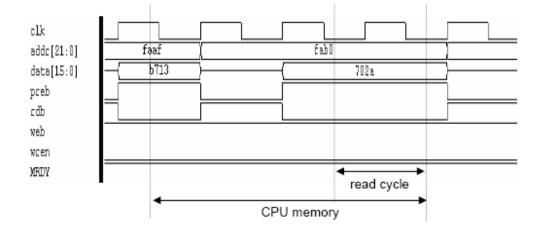

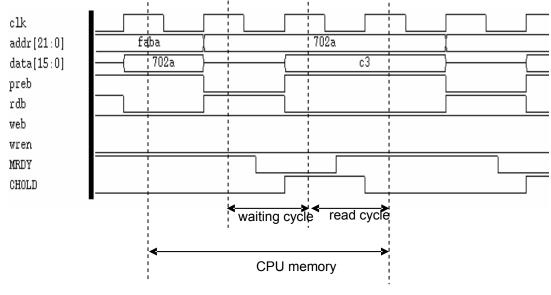

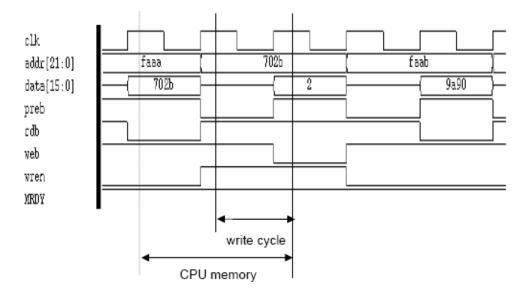

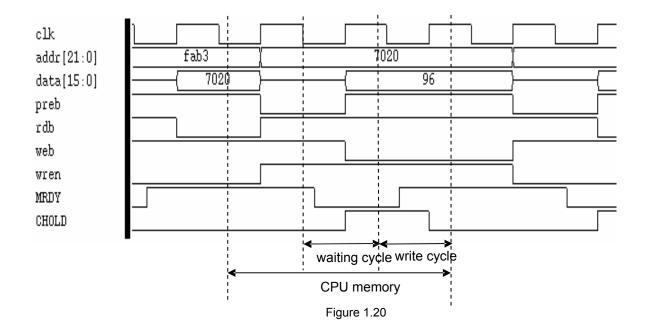

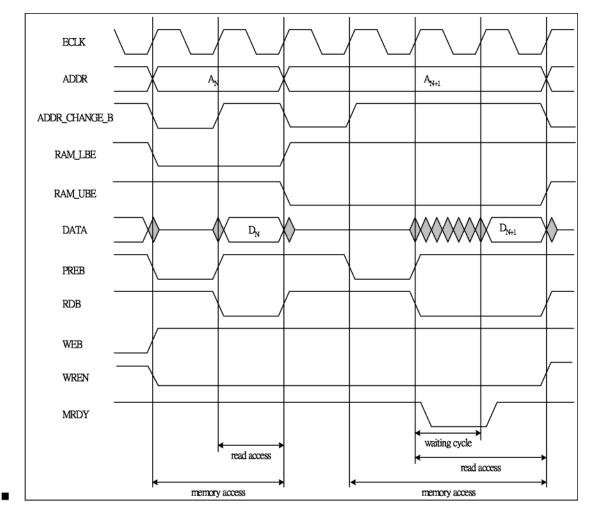

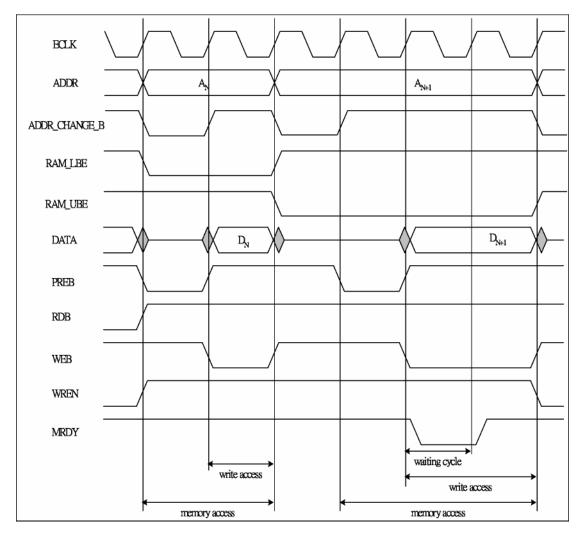

The memory interface of *unSP* 1.2 is an asynchronous interface. Whenever the address transits, the pre-charge (preb) signal will be pulled low 1 cycle to indicated the memory access and the read enable signal (rdb) or write enable signal (web) will be pulled low at next cycle. The CPU may really need data at the second or third cycle after the address transits, so the rdb may be kept 1 cycle or 2 cycles low while reading memory. If the memory bus is not ready for CPU accessing, the memory ready signal (MRDY) must be pulled low to stall CPU accessing before the clock rising edge of rdb or web access cycle. Besides the rdb and web signals, there is an additional signal (wren) indicating the memory read/write accessing within full memory access period. The detail timing diagrams are illustrated as below.

#### Memory read timing without CPU waiting ( 2 cycles)

# Memory read timing without CPU waiting ( 3 cycles)

Memory read timing with CPU waiting (2 cycles)

Figure 1.18

#### Memory write timing without CPU waiting

Figure 1.19

Memory write cycle with CPU waiting

WEB: Memory write enable, changes at clock rising edge, active low.

RDB: Memory read enable, changes at clock rising edge, active low.

PREB: Memory pre-charge signal, changes at clock rising edge, active low.

WREN: Memory write signal, changes within full memory access period, active high.

MRDY: Memory bus ready signal, triggered by external device, must be stable before the clock rising edge of read/write cycle.

CHOLD: CPU internal stall signal.

# 1.6.3 Memory Architecture of unSP-1.3

The memory interface of *unSP* 1.3 is an asynchronous interface. Two cycles are needed for CPU to access memory without external memory wait. At the first cycle, the pre-charge (preb) signal will be pulled low 1 cycle to indicate memory accessing and the read enable signal (rdb) or write enable signal (web) will be pulled low at next cycle. If the memory bus need more cycles to prepare data, the memory bus ready signal (MRDY) should be pulled low to stall CPU accessing before end of read or write cycle. Besides the rdb and web signals, there is an additional signal (wren) indicating the memory read/write accessing within full memory access period. ADDR\_CHANGE\_B indicates the changing of memory address. Byte mode signals RAM\_LBE and RAM\_UBE enable the lower byte and upper byte access, respectively. The detail timing diagrams are illustrated as below.

#### Memory read timing

Figure 1.21

Memory write timing

Figure 1.22

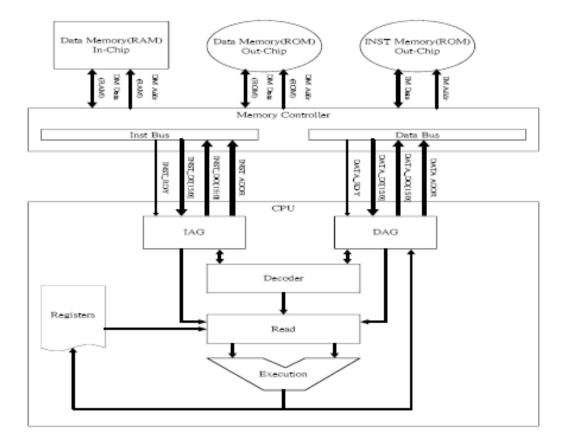

# 1.6.4 Memory Architecture of unSP-2.0

*unSP* 2.0 uses a modified Harvard architecture to accelerate memory access. The memory bus is separated into 2 parts, instruction and data bus. Program executing address is issued at instruction bus and data access address is issued at data bus.

The memory mapping of a real chip may be divided into several parts including internal memory, external memory, I/O memory, ... etc. A memory controller customized by the user is need to manage the memory bus allocation.

Figure 1.23

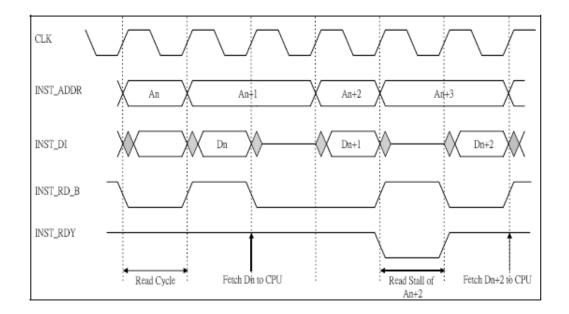

## 1.6.5 Memory Interface of unSP-2.0

Instruction Bus Read Timing

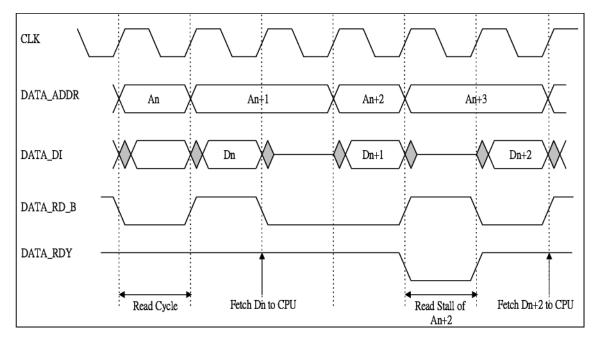

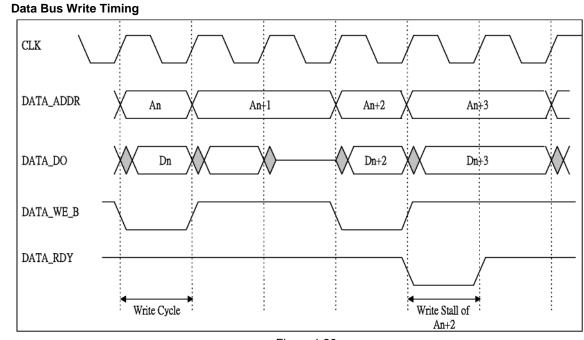

### Data Bus Read Timing

Figure 1.25

Figure 1.26

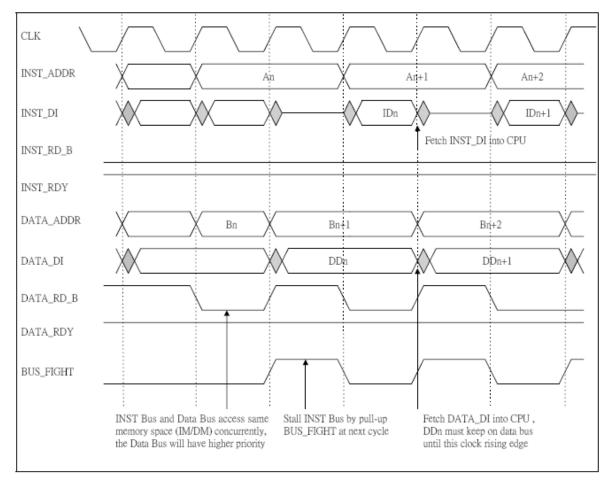

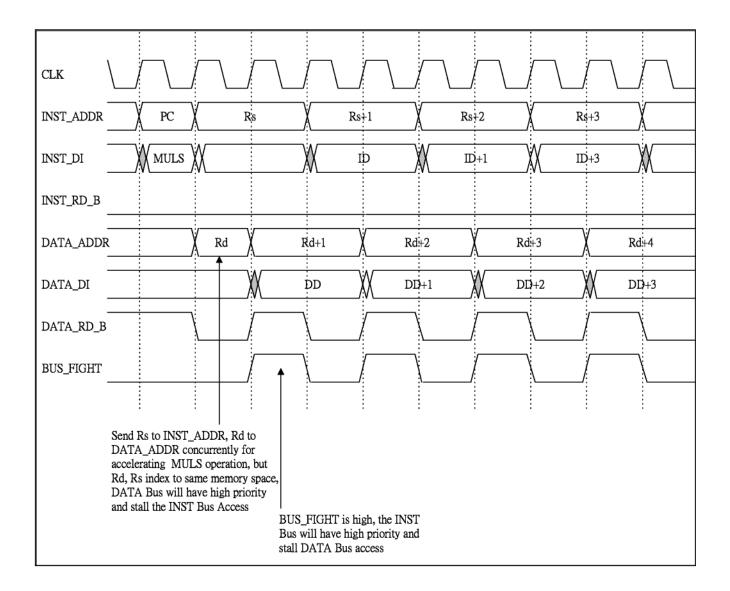

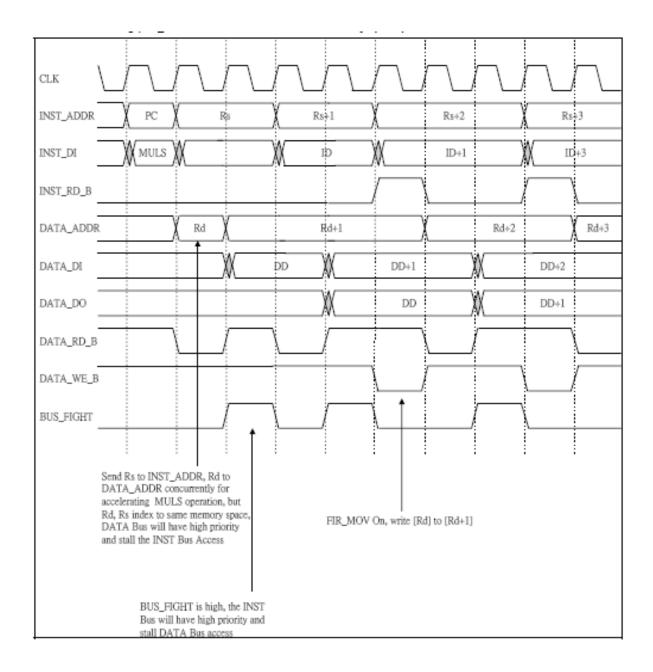

#### INST Bus and Data Bus Access Conflict Timing

If INST Bus and Data Bus access the same memory space (IM/DM) concurrently, the Data Bus will have higher priority than INST Bus. Thus only the Data Bus memory access will be accepted and the memory content of DATA\_ADDR is returned to the bus at next cycle.

The BUS\_FIGHT signal will be pulled high to prevent the INST Bus from getting wrong data at next cycle. If BUS\_FIGHT signal is placed at high then the DATA Bus will release memory bus and let INST Bus to get control of memory bus to prevent starvation condition.

CPU will fetch the data value on INST\_DI and DATA\_DI into internal registers at next clock rising edge while INST\_RDY and DATA\_RDY are high, BUS\_FIGHT is low. So the data input must keep on bus until them being fetched into CPU.

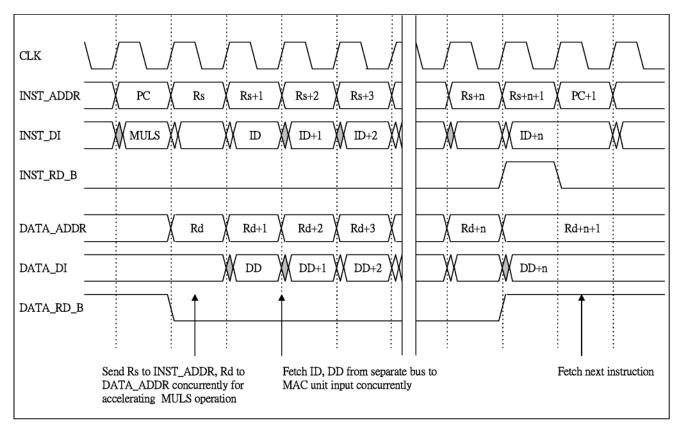

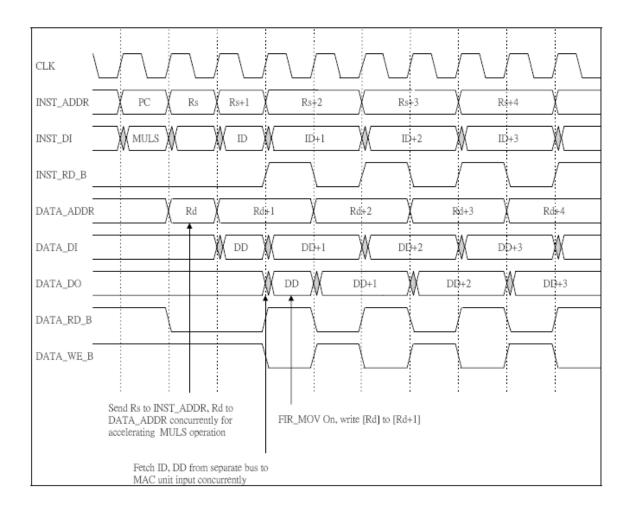

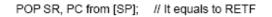

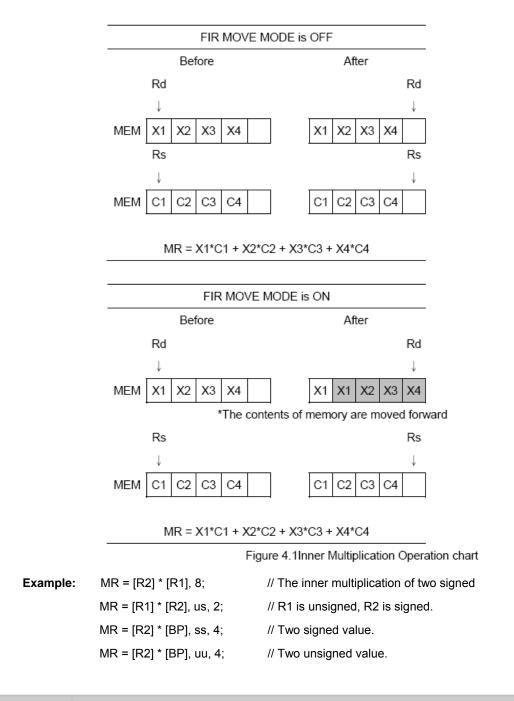

MULS Timing (FIR\_MOV OFF, Rd, Rs index to separate memory space)

MULS operation will fetch data from INST Bus and DATA Bus concurrently to accelerating MAC operation.

If the parameters array location indexed by Rd, Rs are placed at different memory ranges (IM/DM), MULS

will have the best performance. Otherwise, bus conflict stall may be occurred and need 2 times of executing cycles.

Cycles Count:

(No Bus Conflict, FIR\_MOV

OFF): N+2 (No Bus Conflict,

FIR\_MOV ON): 2N+1 (Bus

Conflict, FIR\_MOV OFF):

2N+2 (Bus Conflict,

FIR\_MOV ON): 3N

MULS Timing (FIR\_MOV ON, Rd, Rs index to separate memory space)

Figure 1.29

MULS Timing (FIR\_MOV OFF, Rd, Rs index to same memory space )

Figure 1.30

### MULS Timing (FIR\_MOV ON, Rd, Rs index to same memory space)

Figure 1.31

## **1.7 Addressing Modes**

## 1.7.1 6 addressing modes of *unSP*-1.0 and *unSP*-1.1

In *unSP* 1.0 and *unSP* 1.1, performing the same operation on differently addressed operand may require different addressing modes. This indicates that the final destination address of operand can be derived from register, content in register or offset of address. The destination address formed by some calculations is called Effective Address (EA).

The effective address will be divided into three types according to its number of bit. That is 6-bit, 16-bit and 22-bit EA. The first two are offset of address. Only operand in current page can be addressed. Moreover, the 22-bit EA means all operands in the whole range of memory can be addressed. The *unSP* 1.0 and *unSP* 1.1 supports six addressing modes, in which 16-bit data operand or the address operand of transfer instruction can be accessed. In instruction set, most instructions can combine with these six addressing mode to generate an instruction subset.

- Indexed Address

- Addressing space is limited to the memory in PAGE0 (0x000000-0x00FFFF) only

- PC Relatively

- Program jumps to an address related to PC conditionally or unconditionally. The jumping range is limited to PC±63-word. The condition lies on NZSC flags in SR register.

- In unSP1.1, the jumping range is limited to CS:PC±63-word.

#### Memory Absolute Address

Addressing space is limited to:

- (1) First 64 words  $(0x00 \sim 0x3F)$  in PAGE0

- (2) PAGE0 (0x000000~0x00FFFF)

- (3) Calling a sub-program in code segment of 64-page absolute address

- Immediate

- The operand is IM6 (6-bit immediate value)

- The operand is IM16 (16-bit immediate value)

- Register Direct

The operand is in register directly

- Register Indirect

- Addressing space in memory is limited to data segment in PAGE0 or 64-page addresses. Its

offset depends on content in register and its page index on DS field of SR register.

- Addressing space is limited in PAGE0. The offset depends on the content of register.

- Using register indirect addressing mode in *unSP*1.1, the increment or decrement is the arithmetical operation of 22-bit value, formed by DS register and target register. For instance, suppose R1=0xFFFF. After executing D:[R1++], DS will be incremented by one and R1 becomes 0x0000.

## 1.7.2 6 addressing modes of *unSP*-1.2 and *unSP*-2.0

Register

Users can shift the source register (Rs) value first and then executing ALU operation with destination register (Rd), place the result at destination register.

Immediate

Users can do ALU operation between source register and a 6-bit or a 16-bit immediate value, then

place the result at destination register.

#### Direct

- Users can do ALU operation between source register and the value at memory location indexed by 6-bit or 16-bit operand, then place the result at destination register.

- Users can store register value to a memory location indexed by 6-bit or 16-bit operand.

#### Indirect

- Users can do ALU operation between destination register and the value at memory location indexed by source register, then place the result at destination register.

- Users can store destination register value to a memory location indexed by source register.

- The source register can be increased by 1 before ALU operation or increased/decreased by 1 after ALU operation.

- Users can use the "D:" indicator to access memory location larger than 64k words, if the "D:" indicator is used, the high 6-bit of accessing address will use data segment (DS) value or be zeroed.

#### Multi-indirect

Users can push or pop multiple registers' value to memory location indexed by stack pointer (SP)

#### Displacement

Users can do ALU operation between destination register and the value at memory location indexed by base pointer (BP) with a 6-bit displacement.

## 1.7.3 9 addressing modes of *unSP*-1.3

#### Register

Users can shift the source register (Rs) value first and then executing ALU operation with

destination register (Rd), place the result at destination register.

#### Immediate

Users can do ALU operation between s ource register and a 6-bit or a 16-bit immediate value, then place the result at destination register.

#### Direct

- Users can do ALU operation between source register and the value at memory location indexed by 6-bit or 16-bit operand, then place the result at destination register.

- Users can store register value to a memory location indexed by 6-bit or 16-bit operand.

#### Indirect

- Users can do ALU operation between destination register and the value at memory location indexed by source register, then place the result at destination register.

- Users can store destination register value to a memory location indexed by source register.

- The source register can be increased by 1 before ALU operation or increased/decreased by 1 after ALU operation.

- Users can use the "D:" indicator to access memory location larger than 64k words, if the "D:" indicator is used, the high 6-bit of accessing address will use data segment (DS) value or be

zeroed.

#### Multi-indirect

Users can push or pop multiple registers' value to memory location indexed by stack pointer (SP)

Displacement

Users can do ALU operation between destination register and the value at memory location indexed by base pointer (BP) with a 6-bit displacement.

### Byte Register Indirect

- Users can do ALU operation between destination register and the value at memory location. The first character B or W indicates accessing one byte or word. The effective byte address (abbreviates to EBA) is {Rx+1:Rx}22~0. The effective (word) address is EBA22~1. If Rx0 is 0, low byte in EBA22~1 is the target. If Rx0 is 1, high byte in EBA22~1 is the target.

- When accessing one word and the least significant bit of EBA is 1, that is, accessing across word boundary, a software interrupt occurs and the AdE bit in FR register will be set. User should take care to prevent such unaligned access takes place. If the software interrupt occurs in the developing phase, user should debug their codes to remove unaligned access.

| EA      | Memory Cell | EBA             |

|---------|-------------|-----------------|

| 0x12340 |             | 0x24681 0x24680 |

| 0x12341 |             | 0x24683 0x24682 |

| 0x12342 |             | 0x24685 0x24684 |

| 0x12343 |             | 0x24687 0x24686 |

This addressing mode supports post increment, post increment and pre increment operations on {Rx+1:Rx}22~0. For post increment, post increment and pre increment operations, the bits in {Rx+1:Rx}31~23 (that is, Rx+1 15~7) are not affected.

#### Displacement

Users can do ALU operation between destination register and the value at memory location indexed by base pointer (BP) with a 6-bit displacement.

#### Displacement

Users can do ALU operation between destination register and the value at memory location indexed by base pointer (BP) with a 6-bit displacement.

### 1.8 Interrupts

## 1.8.1 Interrupts of unSP-1.0 and unSP-1.1

unSP 1.0 and unSP 1.1 accept two types of external interrupts: Fast Interrupt (FIQ) and Interrupt

(IRQ). Both interrupts can be freely turned on or off. In addition, *unSP* 1.0 and *unSP* 1.1 also implements a software interrupt, BREAK. The interrupt vector mappings and priorities are depicted as follow:

| Interru | pt Vector |                        | Interrupt Priority                                 |

|---------|-----------|------------------------|----------------------------------------------------|

| 0xFFF5  | BREAK     | 1. Reset (highest)     | * If more than two IRQs occurred simultaneously,   |

| 0xFFF6  | FIQ       | 2. FIQ                 | the priority is from IRQ0 down to UART IRQ.        |

| 0xFFF7  | RESET     | 3. IRQ0 ~ 6, UART IRQ* | That is, IRQ0 is the highest and UART IRQ is       |

| 0XFFF8  | IRQ0      | 4. BREAK** (lowest)    | the lowest. However, if a lower priority IRQ       |

| 0XFFF9  | IRQ1      |                        | occurred first, even a higher priority IRQ can not |

| 0XFFFA  | IRQ2      |                        | interrupt the current IRQ. For example, if IRQ4    |

| 0XFFFB  | IRQ3      |                        | is occurred first, IRQ3 is unable to interrupt     |

| 0XFFFC  | IRQ4      |                        | IRQ4. The priority applies only when two IRQs      |

| 0XFFFD  | IRQ5      |                        | occurred concurrently.                             |

| 0XFFFE  | IRQ6      |                        |                                                    |

| 0XFFFF  | UART IRQ  |                        | **The action of "BREAK" is the same as "CALL"      |

|         |           |                        | except "BREAK" will jump to the fixed address      |

|         |           |                        | specified at 0xFFF5.                               |

#### Figure 1.32

## 1.8.2 Interrupts of *unSP*-1.2

Interrupts are used to handle exception while program is running. *unSP* 1.2 support 10 interrupt sources and 1 reset request. When an exception arises, *unSP* 1.2 completes the current instruction and then departs from the current instruction sequence to handle the exception. The following sequence of actions will be taken by processor before entering service routine.

- According the interrupt priorities to choose the highest priority event. The interrupt priority is showed as below:

- RESET > BREAK > FIQ > IRQ0 > IRQ1 > IRQ2 > IRQ3 > IRQ4 > IRQ5 > IRQ6 > IRQ7

- If IRQ\_NEST mode is off and program running in IRQ service routine, only REST, BREAK and FIQ event can interrupt CPU.

- If IRQ\_NEST mode is on and program running in IRQ service routine, besides RESET, BREAK, FIQ event, the IRQ events with priority greater than PRI register also can interrupt CPU.

- Fetch the relevant vector address list below into CPU.

| Table 1.6 | Table | 1.6 |

|-----------|-------|-----|

|-----------|-------|-----|

| Interrupts |    | TEST | [[1:0] |    |

|------------|----|------|--------|----|

|            | 00 | 01   | 10     | 11 |

| Interrupts | TEST[1:0] |          |          |          |

|------------|-----------|----------|----------|----------|

|            | 00        | 01       | 10       | 11       |

| BREAK      | 0x00FFF5  | 0x00FFE5 | 0x007FF5 | 0x007FE5 |

| FIQ        | 0x00FFF6  | 0x00FFE6 | 0x007FF6 | 0x007FE6 |

| RESET      | 0x00FFF7  | 0x00FFE7 | 0x007FF7 | 0x007FE7 |

| IRQ0       | 0x00FFF8  | 0x00FFE8 | 0x007FF8 | 0x007FE8 |

| IRQ1       | 0x00FFF9  | 0x00FFE9 | 0x007FF9 | 0x007FE9 |

| IRQ2       | 0x00FFFA  | 0x00FFEA | 0x007FFA | 0x007FEA |

| IRQ3       | 0x00FFFB  | 0x00FFEB | 0x007FFB | 0x007FEB |

| IRQ4       | 0x00FFFC  | 0x00FFEC | 0x007FFC | 0x007FEC |

| IRQ5       | 0x00FFFD  | 0x00FFED | 0x007FFD | 0x007FED |

| IRQ6       | 0x00FFFE  | 0x00FFEE | 0x007FFE | 0x007FEE |

| IRQ7       | 0x00FFFF  | 0x00FFEF | 0x007FFF | 0x007FEF |

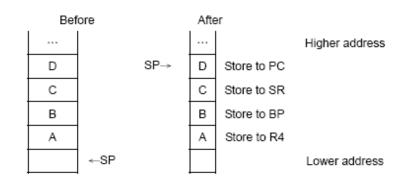

If the interrupt event is IRQ and IRQ\_NEST mode is on, *unSP* will save PC, SR and FR into memory stack indexed by SP. If IRQ\_NEST mode is off, only PC and SR will be saved.

- *unSP* 1.2 will change PC as the address fetched by vector address and fetching the first instruction.

- If the interrupt event is IRQ and IRQ\_NEST mode is on, the PRI register will be changed as the IRQS value.

The leaving sequence of service routine.

If CPU is servicing IRQ interrupt and IRQ\_NEST mode is on, the FR, SR and PC will be restored from memory stack indexed by SP. If IRQ\_NEST mode is off, only SR and PC will be restored. Since the values in these registers are changed by the restore operation, CPU will return to the program status before interrupt and keep executing.

The interrupt timing diagrams are illustrated as below:

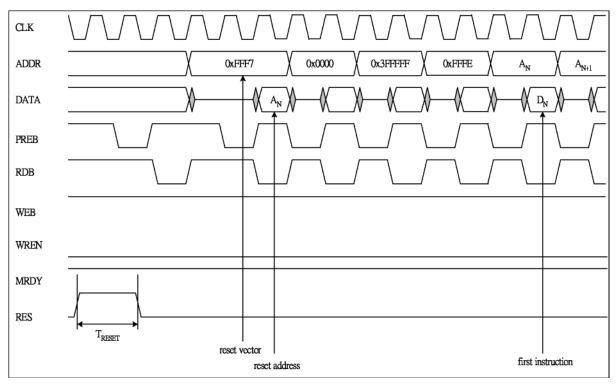

### Reset timing

T<sub>reset</sub>

reset vector

first instruction

### Figure 1.33

- After CPU acknowledge reset signal, the first instruction will be fetched at 10th clock cycle. Program reset vector must place at address 0xFFF7.

- Res: CPU reset signal, active low, Treset Pulse width must keep at least 2 clock cycles for CPU to acknowledge reset pulse.

- fully\_res: CPU internal reset signal.

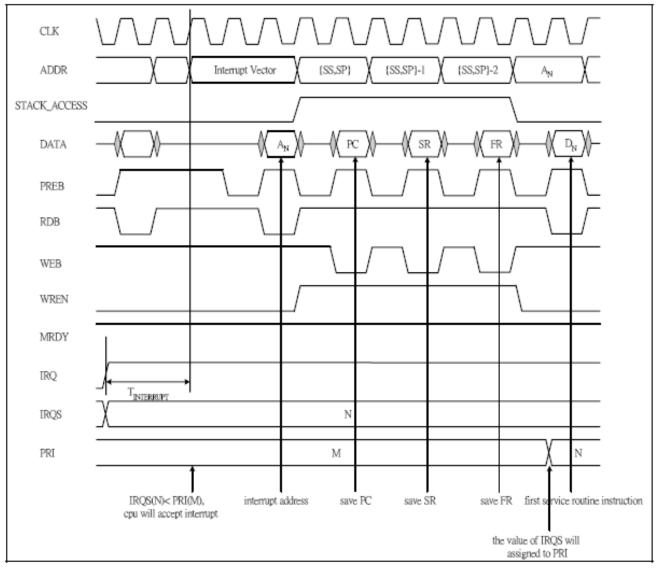

### Entering interrupt service routine

Figure 1.34

### Leaving interrupt service routine

- 8 clock cycles needed from CPU accept interrupt signal to get the first instruction of interrupt service routine.

- The longest delay from interrupt signal rising to acknowledge by CPU Tinterrupt <= 182 clock cycles (max instruction executing cycle)

#### Entering interrupt service routine

- Irqs[2:0]: External interrupt source select pins.

- RQPRI[3:0]: Interrupt priority register, user can change its value to allow specify range of interrupts can be accepted by CPU. After entering interrupt service routine, the IRQPRI register will be change to current IRQ number.

### 1.8.3 Interrupts of *unSP-*1.3

Interrupts are used to handle exception while program is running. *unSP* 1.3 support 10 interrupt sources and 1 reset request. When an exception arises, CPU will complete the current instruction and then departs from the current instruction sequence to handle the exception. The following sequence of actions will be

taken by processor before entering service routine.

- According the interrupt priorities to choose the highest priority event. The interrupt priority is showed as below

- 1. RESET > BREAK > FIQ > IRQ0 > IRQ1 > IRQ2 > IRQ3 > IRQ4 > IRQ5 > IRQ6 > IRQ7

- IRQ\_NEST mode is always on. When program is running in IRQ service routine, besides RESET, BREAK, FIQ event, the IRQ events which priority greater than PRI register also can interrupt CPU.

| Interrupts | Vector Address                                   |

|------------|--------------------------------------------------|

| BREAK      | { ~TEST[1], INT_BASE[9:0], ~TEST[0], 1'h0, 3'h5} |

| FIQ        | { ~TEST[1], INT_BASE[9:0], ~TEST[0], 1'h0, 3'h6} |

| RESET      | { ~TEST[1], INT_BASE[9:0], ~TEST[0], 1'h0, 3'h7} |

| IRQ0       | { ~TEST[1], INT_BASE[9:0], ~TEST[0], 1'h1, 3'h0} |

| IRQ1       | { ~TEST[1], INT_BASE[9:0], ~TEST[0], 1'h1, 3'h1} |

| IRQ2       | { ~TEST[1], INT_BASE[9:0], ~TEST[0], 1'h1, 3'h2} |

| IRQ3       | { ~TEST[1], INT_BASE[9:0], ~TEST[0], 1'h1, 3'h3} |

| IRQ4       | { ~TEST[1], INT_BASE[9:0], ~TEST[0], 1'h1, 3'h4} |

| IRQ5       | { ~TEST[1], INT_BASE[9:0], ~TEST[0], 1'h1, 3'h5} |

| IRQ6       | { ~TEST[1], INT_BASE[9:0], ~TEST[0], 1'h1, 3'h6} |

| IRQ7       | { ~TEST[1], INT_BASE[9:0], ~TEST[0], 1'h1, 3'h7} |

Fetch the relevant vector address list below into CPU.

If the interrupt event is IRQ or FIQ, *unSP*1.3 will save PC, SR and FR into memory stack indexed by {SS, SP}. For RESET and BREAK, only PC and SR will be saved.

- *unSP* 1.3 will change PC as the address fetched by vector address and fetching the first instruction.

- If the interrupt event is IRQ, the PRI register will be changed as the IRQ's value.

- IRQ\_ENABLE is turned off automatically when *unSP* 1.3 performing IRQ service routine. User can

turn on IRQ\_ENABLE in IRQ service routine to allow higher priority IRQ to interrupt it.

- unSP 1.3 can re-execute FIQ service routine when serving FIQ if FIQ\_ENABLE is on. Both FIQ\_ENABLE and IRQ\_ENABLE are turned off automatically when unSP1.3 performing FIQ service routine.

- *unSP*1.3 will check the interrupt signals (FIQ/IRQ) at the last cycle of every instruction **except**:

- RA16 (Direct16 instruction with read) for semaphore implementation of the operating system

- RETI instruction

- MDS access instruction

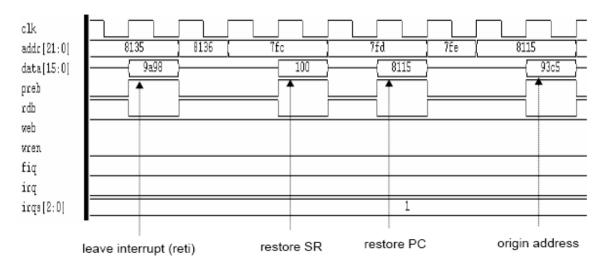

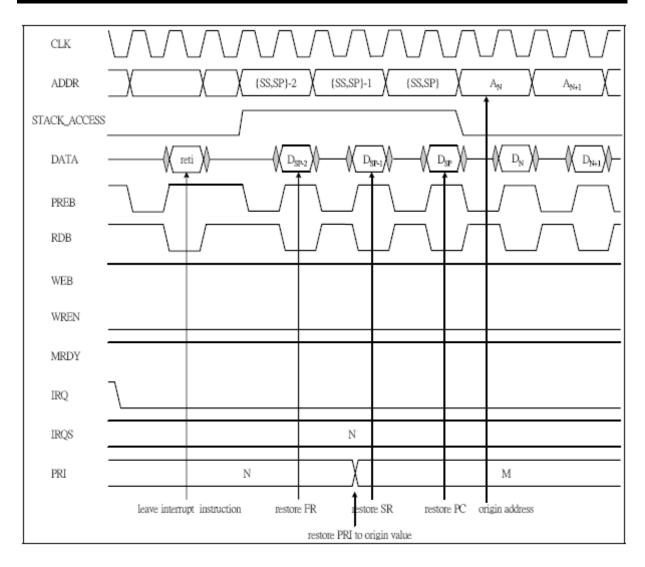

The leaving sequence of service routine.

If CPU is servicing IRQ or FIQ, the FR, SR, PC will be restored from memory stack indexed by SP else only SR, PC will be restored. CPU will return to the program status before interrupt and keep executing.

#### The interrupt timing diagrams are illustrated as below.

#### Reset timing

#### Figure 1.38

- After CPU acknowledge reset signal, the first instruction will be fetched at 12th clock cycle.

- program reset vector must place at address 0xfff7

- RES : CPU reset signal, active high, TRESET pulse width must keep at least 2 clock cycles

#### Entering interrupt service routine

- 10 clock cycles needed from CPU accept interrupt signal to get the first instruction of interrupt service routine.

- The longest delay from interrupt signal rising to acknowledge by CPU TINTERRUPT <= 182 clock cycles (max instruction executing cycle)

- IRQS[2:0]: External interrupt source select pins.

- PRI[3:0]: Interrupt priority register, user can change its value to allow specify range of interrupts can be accepted by CPU. After entering interrupt service routine, the IRQPRI register will be change to current IRQ number.

- Leaving interrupt service routine

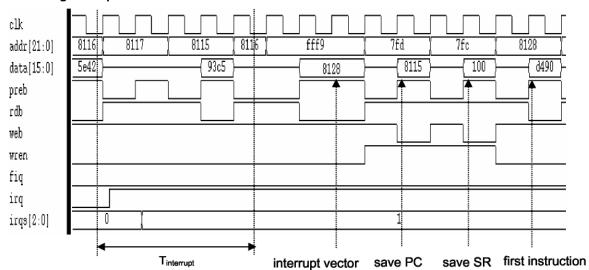

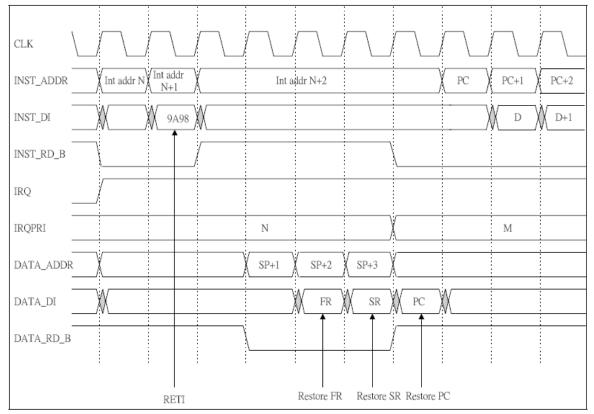

## 1.8.4 Interrupts of unSP-2.0

*unSP* 2.0 supports 10 interrupt sources and 1 reset request. When an exception arises, *unSP* 2.0 completes the current instruction and then departs from the current instruction sequence to handle the exception. The following sequence of actions will be taken by processor before entering service routine.

- According the interrupt priorities to choose the highest priority event. The interrupt priority is shown as below:

- RESET> BREAK > FIQ > IRQ0 > IRQ1 > IRQ2 > IRQ3 > IRQ4 > IRQ5 > IRQ6 > IRQ7

- If IRQ\_NEST mode is off and program running in IRQ service routine, only RESET BREAK, FIQ event can interrupt CPU.

- If IRQ\_NEST mode is on and program running in IRQ service routine, besides RESET, BREAK, FIQ event, the IRQ events which priority greater than PRI register also can interrupt CPU.

Fetch the relevant vector address list below into CPU.

|             | 1         | Table 1.8 |                   |          |

|-------------|-----------|-----------|-------------------|----------|

|             | TEST[1:0] |           |                   |          |

| Interru pts | 00        | 01        | 10                | 11       |

| BREAK       | 0x00FFF5  | 0x00FFE5  | 0x007FF5          | 0x007FE5 |

| FIQ         | 0x00FFF6  | 0x00FFE6  | FE6 0x007FF6 0x00 |          |

| RESET       | 0x00FFF7  | 0x00FFE7  | 0x007FF7          | 0x007FE7 |

| IRQ0        | 0x00FFF8  | 0x00FFE8  | 0x007FF8 0x007    |          |

| IRQ1        | 0x00FFF9  | 0x00FFE9  | 0x007FF9          | 0x007FE9 |

| IRQ2        | 0x00FFFA  | 0x00FFEA  | 0x007FFA          | 0x007FEA |

| IRQ3        | 0x00FFFB  | 0x00FFEB  | 0x007FFB          | 0x007FEB |

| IRQ4        | 0x00FFFC  | 0x00FFEC  | 0x007FFC          | 0x007FEC |

| IRQ5        | 0x00FFFD  | 0x00FFED  | 0x007FFD          | 0x007FED |

| IRQ6        | 0x00FFFE  | 0x00FFEE  | 0x007FFE          | 0x007FEE |

| IRQ7        | 0x00FFFF  | 0x00FFEF  | 0x007FFF          | 0x007FEF |

- If the interrupt event is IRQ and IRQ\_NEST mode is on, *unSP*2.0 will save PC, SR, FR into memory stack indexed by SP else only PC, SR will be saved.

- *unSP* 2.0 will change PC as the address fetched by vector address and fetching the first instruction.

- If the interrupt event is IRQ and IRQ\_NEST mode is on, the PRI register will be changed to current IRQ number.

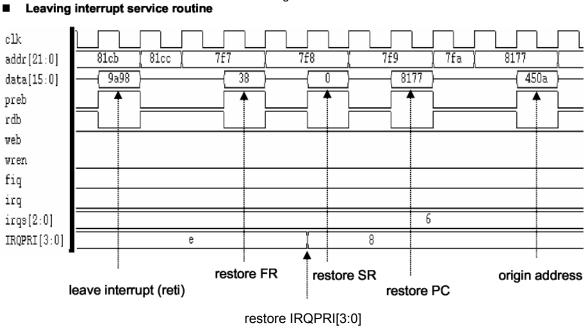

The leaving sequence of service routine.

If CPU is servicing IRQ interrupt and IRQ\_NEST mode is on, the FR, SR, PC will be restored from memory stack indexed by SP else only SR, PC will be restored, and CPU will return to the program status before interrupt and keep executing.

The interrupt timing diagrams are illustrated as below:

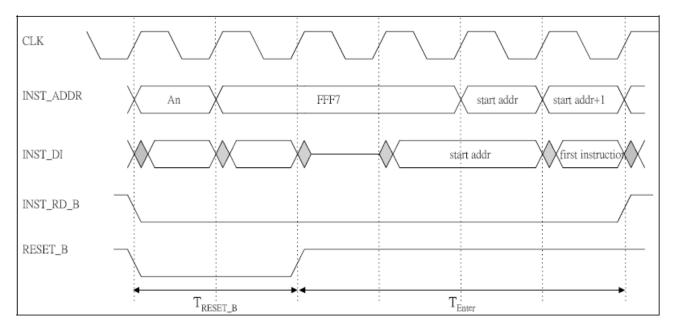

### RESET Timing

Figure 1.41

$T_{{\tt RESET\_B}}$  External reset signal, active low,  $T_{{\tt RESET\_B}}$  pulse width must keep at least 2 clock cycles for CPU

to acknowledge reset pulse.

T<sub>Enter:</sub> Reset timing, 4 cycles needed from CPU accept reset signal to fetch the first instruction.

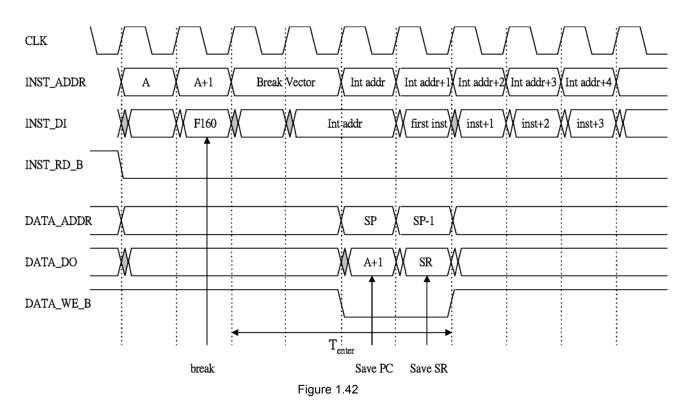

### Break Timing

T<sub>enter</sub>: Interrupt entering time, 4 cycles needed from CPU accept interrupt request to fetch the first instruction.

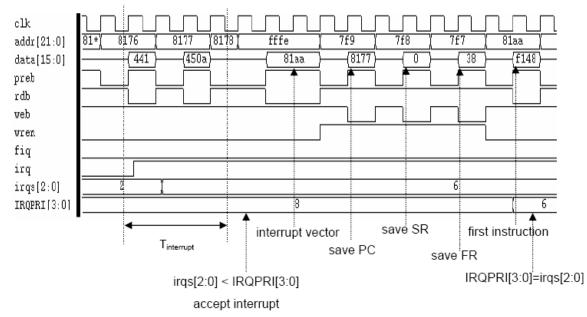

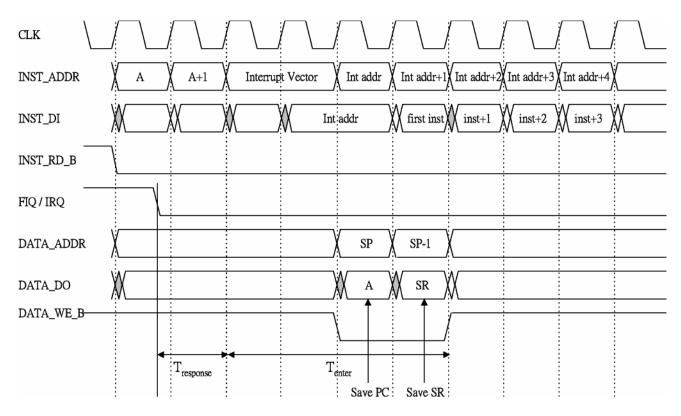

### ■ Entering interrupt service routine

T<sub>respose</sub>: Interrupt Response Time, T<sub>respose</sub> <= 50 clock cycles (max instruction executing cycles, MULS) T<sub>enter</sub>: Interrupt entering time, 4 cycles needed from CPU accept interrupt request to fetch the first instruction.

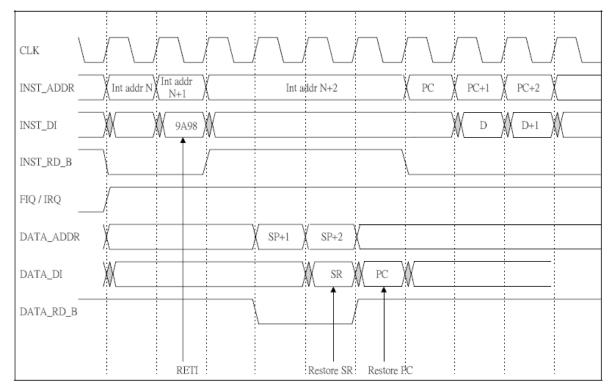

Leaving interrupt service routine

Figure 1.44

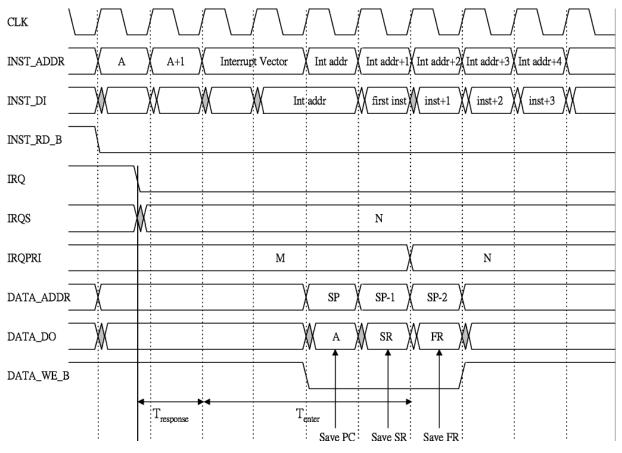

Entering interrupt service routine

Figure 1.45

T<sub>respose</sub>: Interrupt response time, T<sub>respose</sub> <= 50 clock cycles (max instruction executing cycles, MULS). T<sub>enter</sub> : Interrupt entering time, 5 cycles needed from CPU accept interrupt request to fetch the first instruction.

IRQS[2:0]: External triggered IRQ number.

IRQPRI[3:0]: Internal interrupt priority register, user can change its value in FR to disable interrupts with lower interrupt priority. After entering interrupt service routine, the IRQPRI register will be changed to current IRQ number.

Leaving interrupt service routine

## 1.9 Data Types

The data structure of unSP is a 16-bit data type, called a word. A 6-bit constant data type in machine code is for quick access to the first 64 words (0x000000 ~ 0x00003F) in PAGE0. The 6-bit constant also serves as an offset to branch instructions or pointer type (via Base Pointer, BP) data access. The 22-bit constant data type in machine code is for referencing an address in memory. There is no 8-bit data type in unSP.

## 1.10 ALU Operation Types

The ALU operation types and its effect on the flags in SR (Status Register) are listed in Table 1.9.

| Operation Type      | Operation   | Ν | Z | S | С |

|---------------------|-------------|---|---|---|---|

| Add                 | a + b       | ~ | ~ | ~ | ~ |

| Add with carry      | a + b + C   | ~ | ~ | ~ | ~ |

| Subtract            | a + ~ b + 1 | ~ | ~ | ~ | ~ |

| Subtract with carry | a + ~ b + C | ~ | ~ | ~ | ~ |

| Compare             | a + ~ b + 1 | ~ | ~ | ~ | ~ |

Table 1.9 ALU opcode definition

| Operation Type                           | Operation | Ν | Z | S | С |

|------------------------------------------|-----------|---|---|---|---|

| Negative                                 | ~ b + 1   | ~ | ~ | - | - |

| Exclusive OR                             | a XOR b   | ~ | ~ | - | - |

| OR                                       | a OR b    | ~ | ~ | - | - |

| AND                                      | a AND b   | ~ | ~ | - | - |

| Test                                     | TEST a, b | ~ | ~ | - | - |

| Load from memory or register to Register | a = b     | ~ | ~ | - | - |

| Store from register to memory            | a = b     | - | - | - | - |

N, Z, S, C: Negative, Zero, Sign, and Carry.

The flags are defined as follows.

Flag N is 1: if the MSB (most significant bit) of result is 1.

Flag N is 0: if the MSB (most significant bit) of result is 0.

Flag Z is 1: if the result is 0.

Flag Z is 0: if the result is not 0.

Flag S is 1: if the result is negative (for two's complement).

Flag S is 0: if the result is not negative.

Flag C is 1: if carry occurs.

Flag C is 0: if no carry occurs.

For unsigned operations, the largest number for 16-bit representation is 0xFFFF (65535). If the results are greater than 0xFFFF (65535), flag C is set. For two's complement operations, the largest number is 0x7FFF (32767) and the smallest is 0x8000 (-32768). If the computation result is less than zero, flag S is set. However, the result could be larger than 0x7FFF or smaller than 0x8000. For example, 0x7FFF (32767) + 0x7FFF (32767) = 0xFFFE (65534). The result is positive (S=0) and no carry is set (C=0). In this case, the N flag is set (N=1 since the MSB of the result is 1). Overflow occurs if flag N and S are different, either S=0, N=1 or vice versa. In operation, the flags will not be changed if the destination register is PC.

### **1.11 Conditional Branches**

Conditional branches consult flags. Four bits (Opcode, bits 15:12) in the branch type instructions are defined in Table 1.10.

| Syntax | Description                    | Branch |

|--------|--------------------------------|--------|

| JCC    | Carry clear                    | C==0   |

| JB     | Below (unsigned)               | C==0   |

| JNAE   | Not above and equal (unsigned) | C==0   |

Table 1.10 OP codes in conditional branch operations

| Syntax | Description                    | Branch              |

|--------|--------------------------------|---------------------|

| JCS    | Carry set                      | C==1                |

| JNB    | Not below (unsigned)           | C==1                |

| JAE    | Above and equal (unsigned)     | C==1                |

| JSC    | Sign clear                     | S==0                |

| JGE    | Great and equal (signed)       | S==0                |

| JNL    | Not less (signed)              | S==0                |

| JSS    | Sign set                       | S==1                |

| JNGE   | Not great than (signed)        | S==1                |

| JL     | Less (signed)                  | S==1                |

| JNE    | Not equal                      | Z==0                |

| JNZ    | Not zero                       | Z==0                |

| JZ     | Zero                           | Z==1                |

| JE     | Equal                          | Z==1                |

| JPL    | Plus                           | N==0                |

| JMI    | Minus                          | N==1                |

| JBE    | Below and equal (unsigned)     | Not (Z==0 and C==1) |

| JNA    | Not above (unsigned)           | Not (Z==0 and C==1) |

| JNBE   | Not below and equal (unsigned) | Z==0 and C==1       |

| JA     | Above (unsigned)               | Z==0 and C==1       |

| JLE    | Less and equal (signed)        | Not (Z==0 and S==0) |

| JNG    | Not great (signed)             | Not (Z==0 and S==0) |

| JNLE   | Not less and equal (signed)    | Z==0 and S==0       |

| JG     | Great (signed)                 | Z==0 and S==0       |

| JVC    | Not overflow (signed)          | N == S              |

| JVS    | Overflow (signed)              | N != S              |

| JMP    | Unconditional branch           | Always              |

# 2 unSP-1.1 Instruction Set

## 2.1 unSP Instructions Classification

## 2.1.1 Notation

| The following notation | s will be effective in the following chapters of instruction set description.  |

|------------------------|--------------------------------------------------------------------------------|